패키징의 구성, 그리고 방식의 변화

[테크월드=선연수 기자]

반도체의 8대 공정 중 마지막 패키징(Packaging) 공정은 만화 영화에서 로봇에 생명을 불어넣듯 전기적인 신호가 통할 수 있도록 연결해주는 과정이다. 각기 다른 온도, 습도, 진동, 전압 등의 환경에서 파손되기 쉬운 칩을 보호하는 역할도 한다. 반도체의 피부와도 같은 패키징 공정의 주요 구성 요소, 공정 과정, 종류를 알아보자.

반도체 패키징 구성 요소

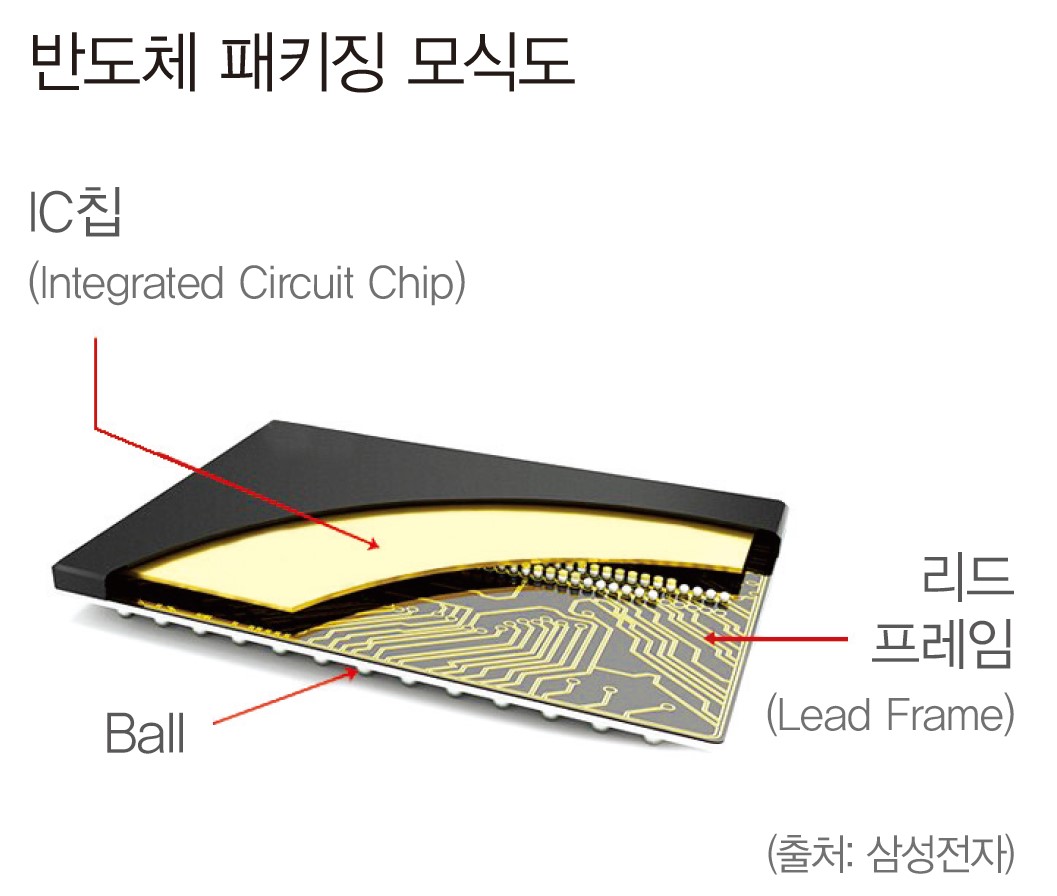

반도체 패키지는 실리콘(Si) 칩, 기판, 금속선이나 범프, 솔더볼(Solder Ball)이나 리드프레임(Lead Frame), 몰딩 컴파운드, 접착제 등으로 이뤄져있다.

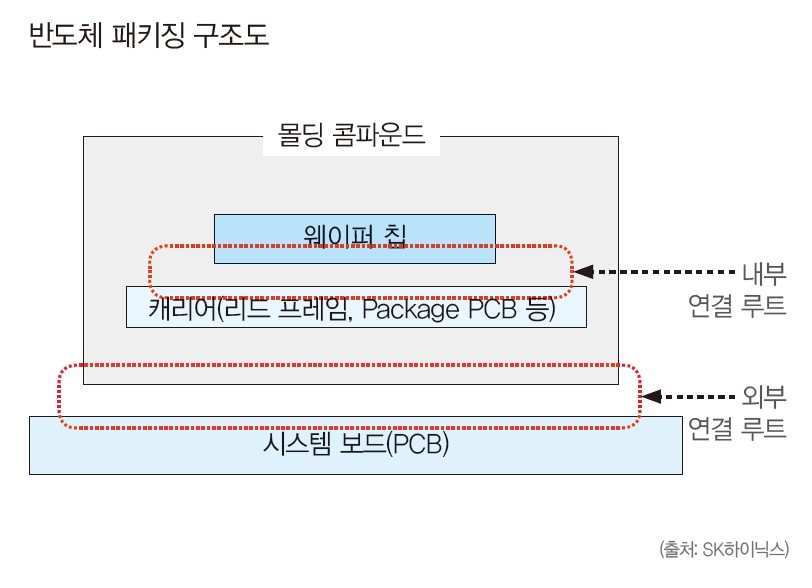

먼저 기판은 반도체 칩을 실장하는 용기다. 칩과 메인 PCB 간 전기적 연결 통로이며, 절연층 위에 도체를 배열한 구조를 가진다.

금속선은 반도체 칩과 기판 사이를 실제적으로 연결하는 선이다. 금(Au), 구리(Cu) 배선이 많이 사용되고 있으며, 최근에는 선의 형태가 아닌 돌기 형태의 범프(Bump)로 연결하는 방식이 주로 채택되고 있다.

솔더볼은 기판과 PCB를 연결하는 장치다. 이전에는 리드프레임에 기반한 패키지를 활용했으나(지금도 일부 사용되고 있다) 현재는 솔더볼을 주로 이용하고 있다. 솔더볼은 패키지 변형 시 열팽창 차이로 접합부에 크랙이 발생할 수 있어 열팽창 차이를 줄여 수명을 늘리는 것이 개발 과제 중 하나다.

몰딩 컴파운드는 칩을 마지막으로 감싸 부품을 고정하는 용도다. 주로 세라믹, 금속, 플라스틱이 사용되며, 가격적인 이유로 플라스틱이 선호된다. 에폭시 수지에 실리카와 같은 무기재료와 경화재, 난연재, 이형제와 같은 각종 부재료가 첨가된 EMC(Epoxy Molding Compound)가 주로 사용된다. 이는 외부의 충격, 진동, 침식 등의 직접적인 보호를 위한 과정이다.

연결 또 연결, 패키징 과정

일반적으로 패키징은 웨이퍼 소잉(Sawing) – 다이 부착 – 와이어 본딩 – 몰딩(Molding) – 마킹(Marking) – 볼(Ball) 부착 – 패키지 소잉 – 패킹(Packing)의 과정을 거친다.

소잉은 웨이퍼에 만들어진 수백 개의 다이를 다이아몬드 소우(Saw)와 같은 장비를 이용해 스크라이브 라인을 따라 잘라내는 과정이다. 이렇게 분리된 칩을 다이라고 부르며, 이 다이는 리드프레임이나 PCB 위에 부착된다. 이후 반도체 칩에 전기가 연결되도록, 내부 연결 루트에서 칩의 접점과 기판의 접점을 금속선으로 연결해준다. 예전에는 금속선을 많이 사용했지만, 최근엔 볼(범프) 형태로 연결하는 본딩 방식을 많이 활용하고 있다. 범프는 전기저항이 더 작아 더 빠른 전기 전달력 성능을 가지며, 보다 작은 폼팩터로 구현할 수 있도록 돕는다.

이후 몰딩에서는 외부환경으로부터 칩을 보호할 수 있도록 제품에 적합한 화학수지를 택해 패키징한다. 외부의 충격과 습기로부터 칩을 보호하기 위해 경화수지를 사용한다. 이후 레이저로 고유 칩 번호를 기록하는 마킹 과정을 거쳐, 볼을 부착한 뒤 패키지 형태로 잘리게 된다. 최종 패키징까지 마친 제품은 고객사로 이동된다.

4세대에 걸친 패키징 기술의 발전

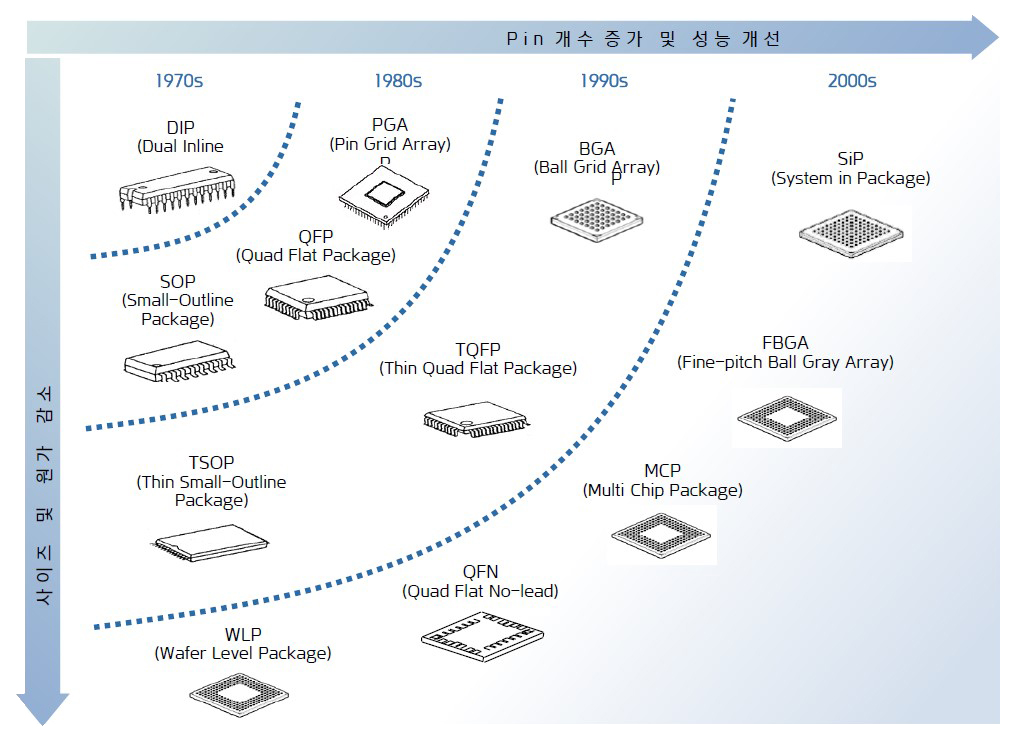

반도체 패키징은 가볍고(경), 얇고(박), 짧고(단), 작은(소), ‘경박단소’를 목적으로 한다. 이에 맞춰 발전해온 반도체 패키징 역사를 총 4세대로 나눠 바라본 NH투자증권의 이세철 분석가의 시각에 입각해 살펴보자.

먼저 1세대는 칩과 패드를 금속선으로 연결하는 리드프레임에 기반한 와이어본딩 방식이 주를 이뤘다. 보호와 연결과 같은 기본 기능에 충실했던 1세대를 지나 점점 집적화된 패키징이 요구됐다. 2세대는 PCB에 기반한 와이어본딩 방식인 FBGA, MCP와 같은 기술이 등장했다.

점점 더 작은 패키지를 추구하게 되면서 금속 와이어의 부피가 문제됨에 따라, 3세대는 돌기인 범프(Bump) 방식의 연결로 전환하게 된다. 솔더볼과 범프 방식이 등장하면서, I/O 단자 수가 많이 늘게 됐고 부품 소형화, 공정 미세화 등으로 플립칩(Flipchip), SIP, WLCSP와 같은 방식이 개발됐다.이는 주로 스마트폰에 많이 활용됐으며, 현재 국내 패키징 업체들의 주 보유 기술도 3세대 패키징 기술이다.

4세대는 패키지 단계에서 여러개의 칩을 통합하는 것이 핵심 기술이다. 더 작아진 면적에 더 많은 칩을 집적하기 위해 적층 기술이 등장했고, 칩을 비롯한 부품들이 통합된 모듈형 패키지도 등장했다. 이에 등장한 TSV(Through Silicon Via)와 같이 칩에 미세한 구멍을 내 연결시키는 기술은 웨이퍼 수준의 공정 기술을 가진 종합 반도체 업체(IDM)나 직접 칩을 생산하는 파운드리 업체에게 유리해, 향후 업체 구조가 바뀔 가능성이 있다는 시각이 있다.

간단히 말하자면, 기존의 방식은 내부 연결은 와이어, 외부 연결은 리드프레임으로 삽입 실장하는 방식이었고, 지금은 내부는 범프, 외부는 솔더볼로 표면 실장을 하는 방식(대표적으로 BGA, Ball Grid Array)으로 변한 것이다. 패키징 기술이 점점 발전하고 칩의 구조에까지 영향을 주고 있어, 다음 세대를 이끌어 갈 혁신적인 아이디어가 무엇일지 궁금해진다.

- 이 글은 테크월드가 발행하는 월간 <EPNC 電子部品> 2020년 6월 호에 게재된 기사입니다.

그래도 삭제하시겠습니까?