적층 기술의 구조와 기업별 기술

[테크월드=선연수 기자]

위로 성장하는 3D 낸드 플래시

낸드 플래시(NAND Flash)란 플래시 메모리의 한 종류로 전원 공급이 되지 않아도 데이터를 보존해 저장·삭제할 수 있다. 이는 셀을 수직으로 배열해 면적이 좁아도 보다 많은 셀을 집적해 설계할 수 있다는 장점을 갖는다. 여기서 셀은 데이터를 저장하는 역할을 한다. 즉, 더 많이 쌓을수록 더 많은 데이터를 저장할 수 있게 되는 것이다.

기존의 2차원 평면 구조의 메모리 공정은 10nm 메모리 공정 기술로 접어들면서 한계에 부딪히기 시작했다. 셀 간 간격이 좁아지면서 전자가 누설되는 간섭현상(Cross talk)이 심해진 것이다. 이런 1층의 구조에서 벗어나 새로운 대안이 된 것이 3D 낸드 플래시 기술이다.

2D 구조와 3D 구조를 흔히 단층 주택과 아파트로 많이 비유하곤 한다. 3D 구조를 통해 저장 용량은 물론, 메모리의 속도, 수명, 전력 효율성도 개선할 수 있으며, 안정성과 내구성 또한 향상시킨다. 이렇게 고도로 셀이 집적된 낸드 플래시는 주로 모바일 기기를 비롯한 전자제품의 저장장치로 많이 활용된다.

3D 낸드는 삼성전자가 2013년 세계 최초로 양산해냈다. 24단 3D 낸드 플래시를 시작으로 36단, 48단, 64단, 72단 적층을 이어와 100단을 넘는 기술이 공개되고 있다.

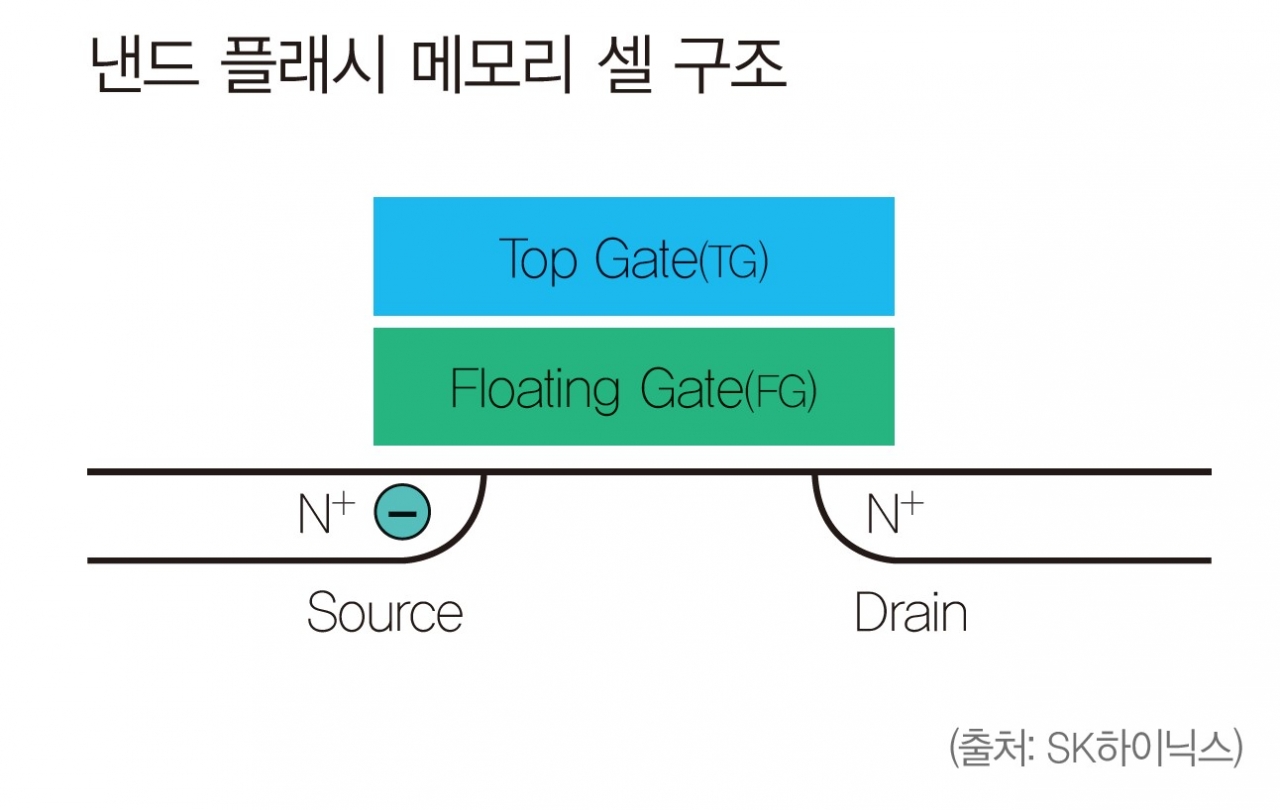

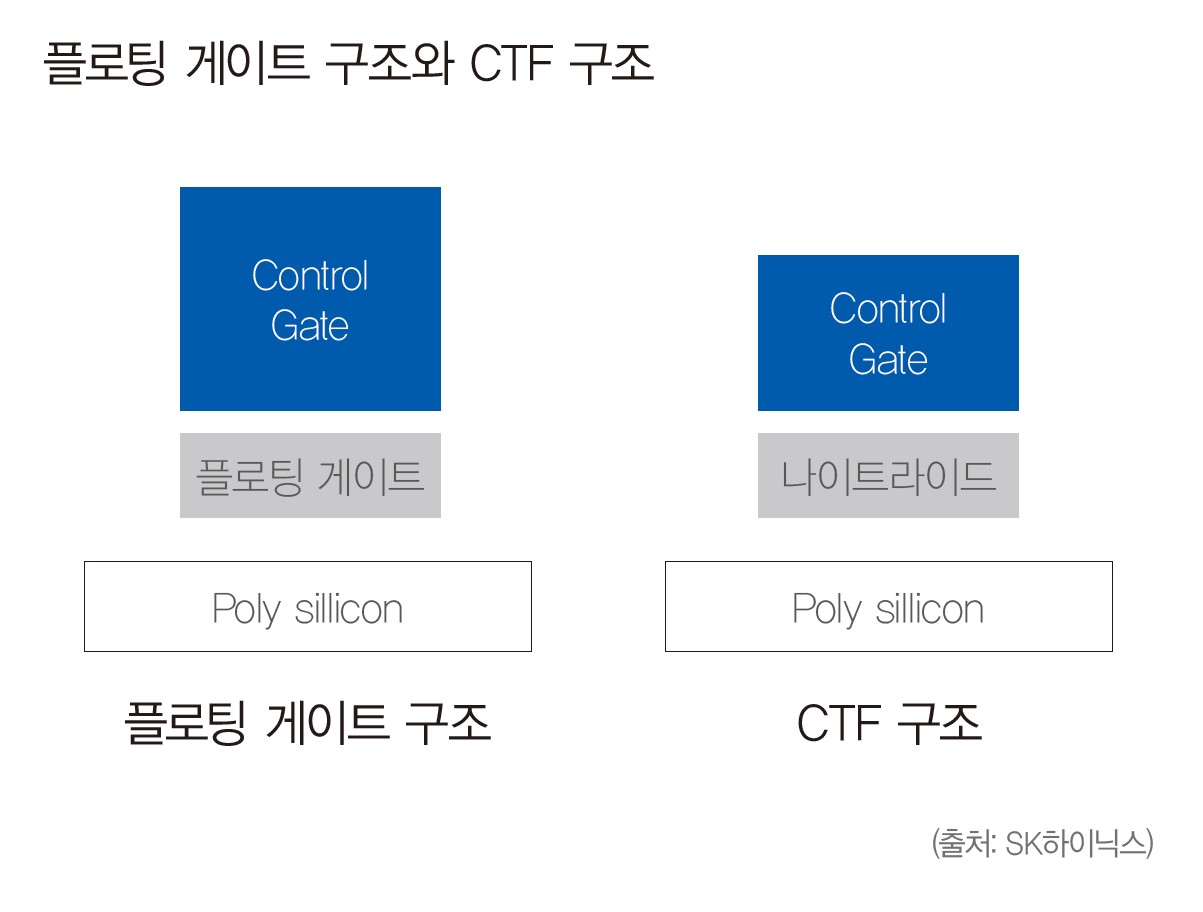

적층에 사용되는 3D 낸드 플래시 증착 기술은 ‘CTF’ 낸드 플래시 기술이라고 불린다. 이는 기존에 사용되던 도체 플로팅게이트(Floating Gate)를 부도체인 CTF가 대신하는 기술이다. 이 CTF를 적층하고 구멍을 뚫어 전하를 채워 넣는 방식으로 데이터를 기록한다.

4D 낸드 플래시? 기업별 각기 다른 적층 방식

기본적으로는 부도체 CTF를 사용한 수직적층 방식으로 낸드 플래시를 구현하지만, 세부적인 기술은 기업마다 차이가 있다. 또한, 96단부터는 증착이나 식각 등 공정의 난이도가 배가 되면서 업체들의 기술 방향도 길을 달리하고 있다.

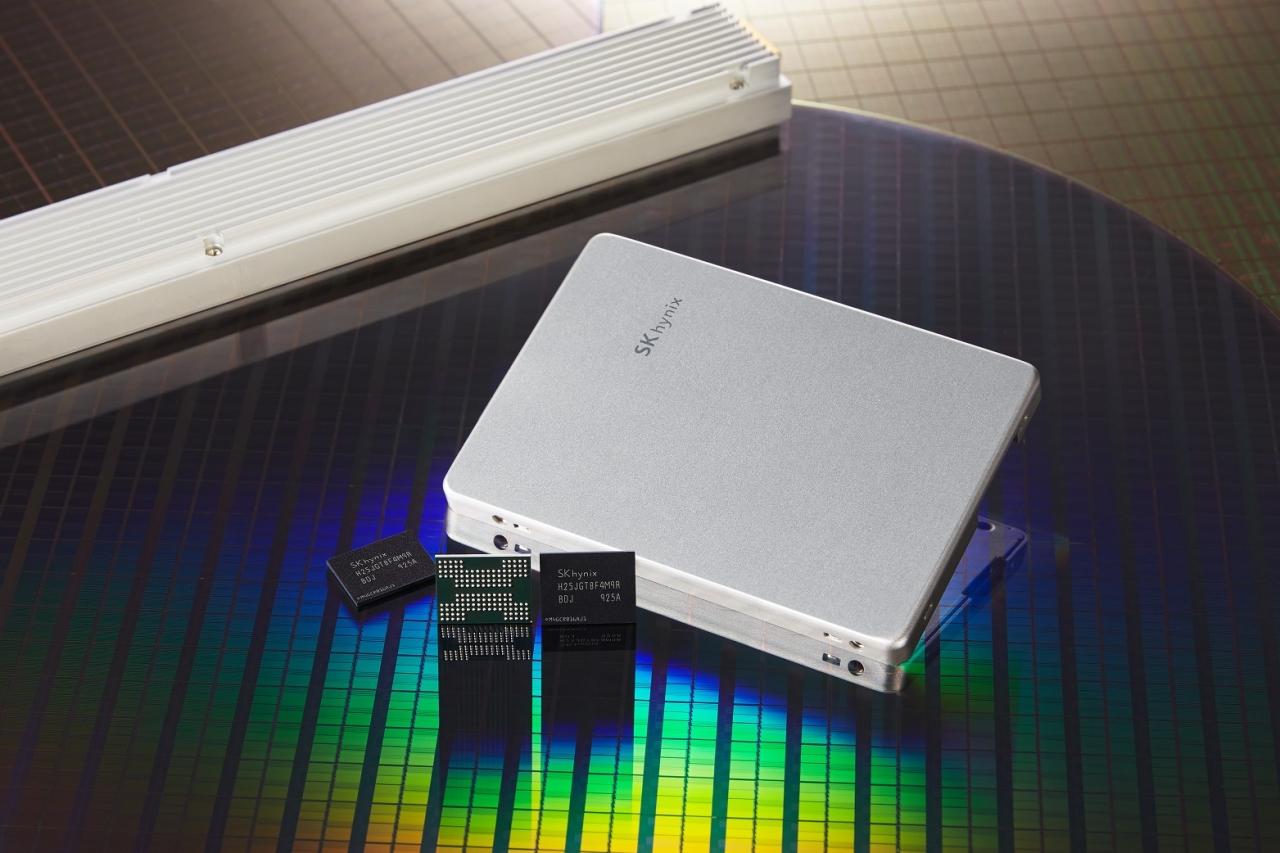

SK하이닉스는 작년 6월 3D를 넘어선 128단 4D 낸드 플래시 기술을 발표했다. 이는 TLC에 기반한 기술로 총 3600개의 셀이 집적돼 1Tb의 용량을 지원한다.

이는 기존에 수직으로 쌓은 셀 옆에 위치했던 주변부 회로(Peri.)를 셀 아래로 집적시키는 기술이다. 주변부 회로는 데이터를 저장하는 셀을 구동하고 입출력을 제어하는 역할을 한다. 2D 낸드 플래시 기술에서는 같은 기판 위에 집적했으나, 3D 공정으로 넘어가면서 두 공정이 분리됐다. 기존에 전체 메모리 면적의 20~30%를 차지하던 주변부 회로를 셀 아래로 집적함으로써 전체 면적을 줄일 수 있게 됐다.

SK하이닉스는 이를 PUC 구조라 부르며, 기존의 3D 낸드 플래시가 아파트라면 4D 낸드 플래시는 아파트 아래에 상가가 있는 주상복합 아파트라고 설명했다.

삼성전자는 작년 8월 6세대 낸드 플래시 기술을 발표했다. 이는 채널 홀 에칭(Channel Hole Etching) 기술을 활용해 기존 5세대 V낸드보다 단수를 약 1.4배 높인 것으로, 전기가 통하는 136단의 몰드(Mold) 층을 올린 형태다. 이 역시 3D CTF셀로 구현된다.

보통은 셀을 많이 쌓을수록 셀 간 절연 상태를 균일하게 유지하기가 어려워, 낸드 플래시의 동작 오류가 늘고 데이터 판독 시간이 지연되는 문제가 발생한다. 삼성전자는 이를 극복하기 위해 초고속 설계 기술을 적용함으로써 데이터 쓰기 시간 450㎲ 이하, 읽기 응답 대기시간 45㎲ 이하의 성능을 이뤄냈다고 밝혔다. 이는 삼성전자의 5세대 낸드 플래시 대비 성능은 10% 증가하고 동작 전압은 15% 이상 줄어든 결과를 나타냈다.

채널 홀은 6.7억 개 미만으로 256Gb 용량을 구현해, 약 9.3억 개의 채널 홀을 가진 5세대 제품 대비 공정 수와 칩 크기를 줄여 생산성도 20% 이상 높일 수 있었다고 삼성전자는 밝혔다.

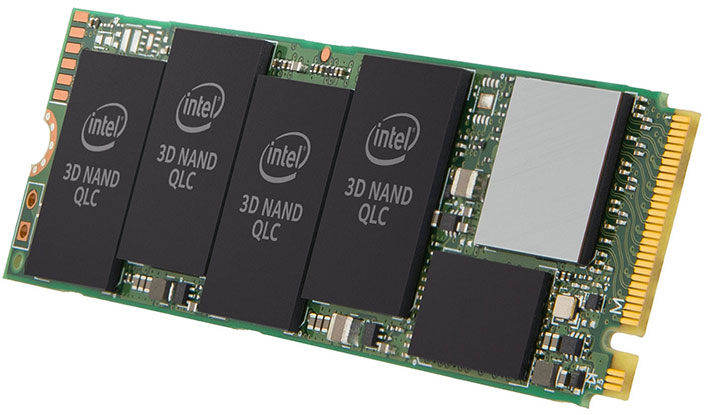

인텔은 작년 9월 ‘메모리&스토리지 데이 2019’에서 144단 3D 낸드플래시를 발표했다. 삼성전자나 SK하이닉스와는 달리, 인텔은 CTF가 아닌 플로팅 게이트에 기반해 3D 낸드 플래시를 제작한다.

인텔은 CTF의 경우 셀을 잡고 있는 어레이를 제어하기 위해 컨트롤 회로를 주변에 수평적으로 배치해야 하나, 플로팅 게이트는 셀 아래쪽에 배치할 수 있기 때문에 비용을 절감할 수 있다고 설명한다. 플로팅 게이트를 사용하면 셀 밀도를 높일 수 있다는 장점이 있다.

인텔의 낸드 플래시 기술은 기존의 TLC 기술에서 한층 더 발전한 QLC를 채택했다는 점에서도 주목받았다. QLC란 셀에 더 많은 정보를 저장할 수 있음을 의미한다. 하나의 셀에 얼마만큼의 비트(bit)를 담을 수 있냐에 따라 SLC(Single Level Cell), MLC(Multiple Level Cell), TLC(Triple Level Cell), QLC(Quad Level Cell) 등으로 분류된다. 셀에 집적되는 비트 수가 높을수록 더 많은 정보를 저장할 수 있다.

- 이 글은 테크월드가 발행하는 월간 <EPNC 電子部品> 2020년 8월 호에 게재된 기사입니다.

그래도 삭제하시겠습니까?