[테크월드=선연수 기자] 스위치 모드 전원 장치(SMPS, Switched-Mode Power Supply)는 전통적인 실리콘(Si, Silicon) MOSFET 기술을 사용해 꾸준히 효율을 높여 왔다. 새로운 실리콘 제조 프로세스, 설계 방법론, 혁신적인 토폴로지를 적용해 한계를 극복해 왔다. 더군다나 지난 몇 년 사이 실리콘 카바이드(SiC, Silicon Carbide)와 같은 와이드 밴드갭 기술이 등장하면서 SMPS의 효율을 더 올릴 수 있게 됐다.

그러나 두 기술 간 가격 차이는 고려해야 할 부분이다. 먼저 출시된 1200V 제품에 이어 650V SiC MOSFET이 출시되면서, 이제는 기존에는 사용할 수 없었던 애플리케이션에 SiC 제품을 적용하는 것을 검토해볼 수 있는 단계에 이르렀다.

SiC의 활용 가능성

SMPS는 다양한 애플리케이션에 사용된다. 범용 전원 장치뿐만 아니라, 태양광, 풍력 발전, 모터 드라이브, 전기차 충전에 이르기까지 다양한 용도에 활용된다. 1000V 이상의 높은 전압대에는 IGBT가 주로 사용돼 왔으나, 특정 분야에서는 SiC가 틈새시장을 파고들고 있다. 특히 고주파 스위칭이 요구되며 높은 전력 밀도를 달성하고자 하는 경우를 예로 들 수 있다.

650V 범위의 SiC는 연속 전도 모드(CCM, Continuous Conduction Mode) 역률 교정(PFC, Power Factor Correction)과 같은 효율이 고도화된 토폴로지를 가능하게 해준다. 이런 토폴로지는 서버, 텔레콤, 배터리 포메이션, EV 충전과 같은 다양한 애플리케이션에 사용하기 적합하며, 이를 통해 시스템 효율, 견고성, 총소유비용(TCO)을 높일 수 있다.

수백 와트(W)에서 수십 킬로와트(kW)에 이르는 저전압 애플리케이션에 SiC의 적용을 고려할 수 있게 되면서, 이제는 어떤 경우에 Si MOSFET을 SiC로 전환하는 것이 좋을지 판단하는 것이 새로운 과제가 됐다.

SiC의 장점

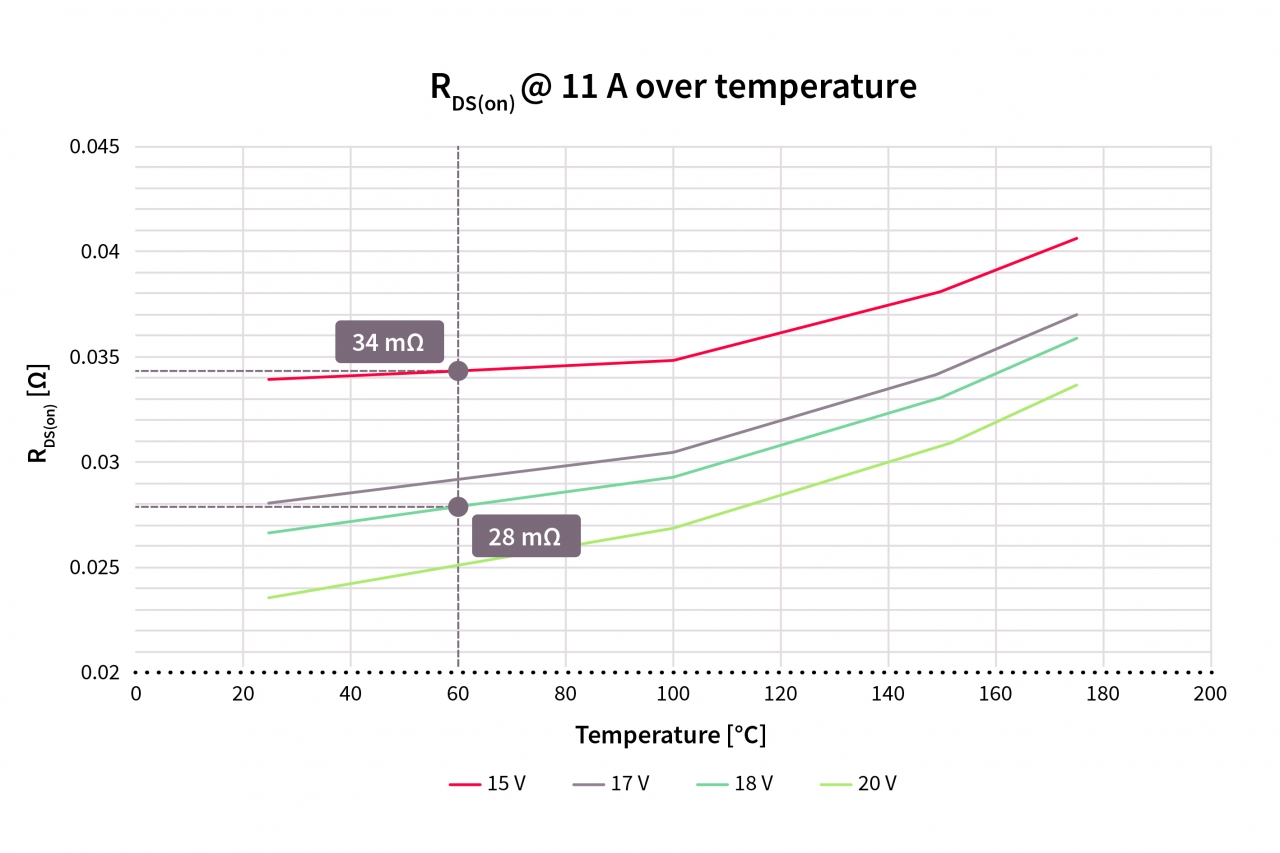

가장 먼저 고려해야 할 점은 애플리케이션이 달성하고자 하는 효율과 전력 밀도다. SiC는 Si MOSFET 대비 동작 온도 범위에 걸쳐 RDS(on)이 훨씬 안정적이다. Si MOSFET은 통상적으로 25℃일 때 최대 RDS(on)을 표기하는데, SiC MOSFET은 25℃와 함께 게이트 구동 전압(정격 18V)과 특정한 전류(ID)로 정격값을 표기한다. CoolMOS 디바이스는 25℃와 100℃ 사이에 RDS(on)이 1.67배 증가하는 것에 비해, 동급 CoolSiC 디바이스는 1.13배만 증가한다. 즉, 84mΩ CoolSiC MOSFET의 목표 동작 온도로 57mΩ CoolMOS 스위치와 전도 손실이 같다는 뜻이다. 높은 온도가 성능에 미치는 영향이 비교적 적기 때문에, 더 높은 밀도로 디자인할 수 있고 필요한 냉각도 줄일 수 있다.

SiC로 전환해도 기존 Si 디바이스에 사용되는 것과 같이 최대 15V에 이르는 게이트 구동 전압을 발생시키는 동일한 드라이버를 사용할 수 있다. 그러나 사용되는 게이트 구동 전압에 따라 RDS(on)도 영향을 받기 때문에, 이와 관련해 약간의 변경이 요구될 수 있다. CoolSiC MOSFET은 0~18V의 게이트 구동 전압을 사용할 수 있어 15V 사용 대비 60℃에서 RDS(on)을 18%까지 낮출 수 있다[그림 1].

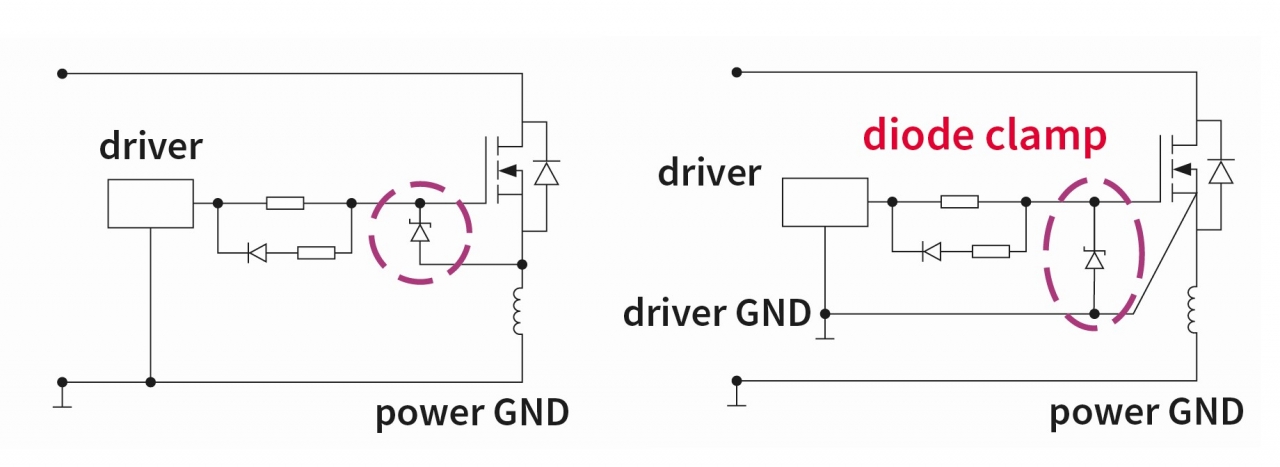

SiC MOSFET 게이트로 음의 전압이 인가되지 않도록 신경 써야 한다. 음의 전압이 인가되면 게이트 임계 전압 VGS(th)로 드리프트를 일으키기 때문이다. 이렇게 되면 장기간 동작할 경우 RDS(on)이 약간 증가할 수 있다.

게이트 구동 루프의 소스 인덕턴스로, 전압 강하로 인한 높은 di/dt 때문에 VGS(off)가 음이 될 수 있다. 하프 브리지 구성으로 이차 스위치의 게이트-드레인 커패시턴스로 인해 매우 높은 dv/dt가 발생될 때도 마찬가지다. dv/dt와 di/dt를 낮춰 문제를 해결할 수 있지만, 이 경우 효율이 떨어진다.

그러므로 스위치의 게이트와 소스 사이에 클램핑 다이오드를 사용하는 것이 좋다. 이를 통해 게이트로 인가되는 음의 전압을 -2V 이상으로 제한함으로써 디바이스를 VGS(th) 드리프트로부터 보호할 수 있다.

필요에 따라 인덕티브 구동 시 영향을 낮출 수 있는 추가적인 조치도 간단히 구현할 수 있다. 이를 위해 드라이버 접지와 전원 접지를 분리해 게이트 구동 루프로부터 소스 인덕턴스를 제거할 수 있다. [그림 2]에서 볼 수 있듯이 켈빈 소스를 사용해 효율을 크게 높일 수도 있다. 특히, 최대 드레인 전류일 때 효율을 많이 증가시킬 수 있다.

역 복구 전하의 영향

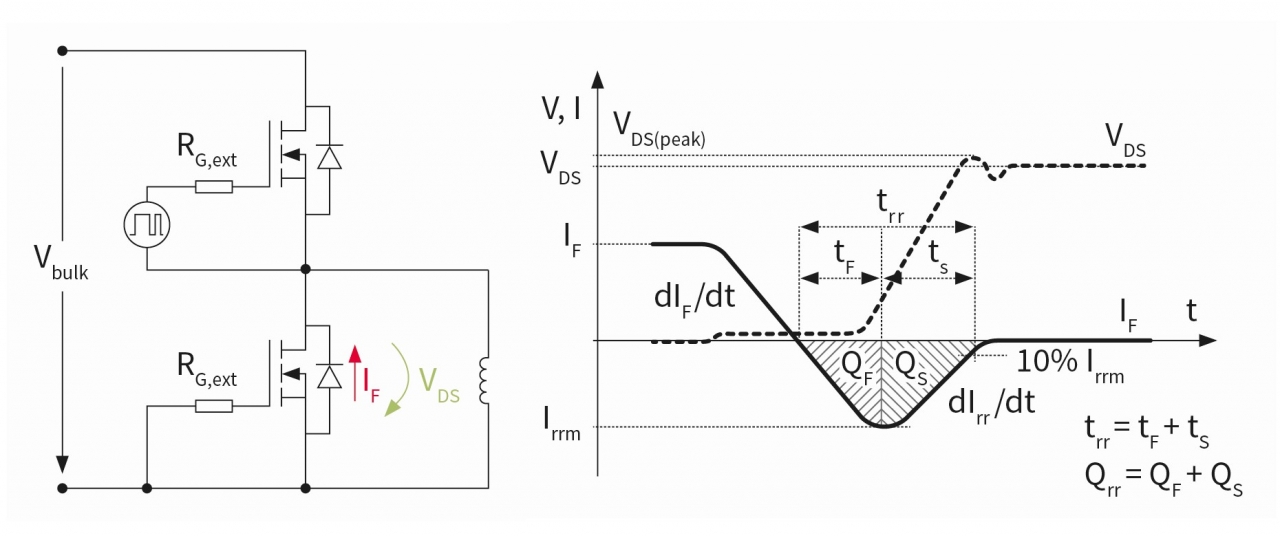

역 복구 전하(Qrr)는 공진 토폴로지나 전도 바디 다이오드로 연속적 하드 정류를 사용하는 디자인에서 특히 중요하게 고려해야 할 파라미터다. 모든 MOSFET은 내부에 바디 다이오드를 포함하고 있으며, Qrr은 전도를 멈춘 후 다이오드부터 제거해야 할 전하를 말한다[그림 3].

반도체 업계는 이 값을 낮추기 위해 노력해 왔으며, CoolMOS 제품 역시 발전을 거듭해오면서 향상된 성능의 고속 바디 다이오드를 포함하고 있다. 이런 노력을 통해 이전 MOSFET 대비 Qrr을 10배가량 낮출 수 있게 됐다. 놀라운 점은 CoolSiC 제품이 최신 고속 다이오드 CoolMOS 제품과 비교해 Qrr을 10배 더 낮춘다는 점이다.

업계에서 50% 부하로 98% 시스템 효율을 달성하고자 함에 따라, PFC 스테이지로 99%나 그 이상의 효율을 달성하는 것이 중요해졌다. 이를 해내지 못하면 원하는 시스템 효율을 달성하기 어려워질 것이다. CoolSiC 스위치를 사용해 Qrr을 높임으로써 PFC로 하드 스위칭 토폴로지를 사용할 수 있게 됐다. CoolMOS 사용 시 권장되는 삼각 전류 모드(TCM, Triangular Current Mode) 기법이 아닌 연속 전도 모드 토템폴 PFC를 사용할 수 있다.

SiC 사용 시 출력 커패시턴스

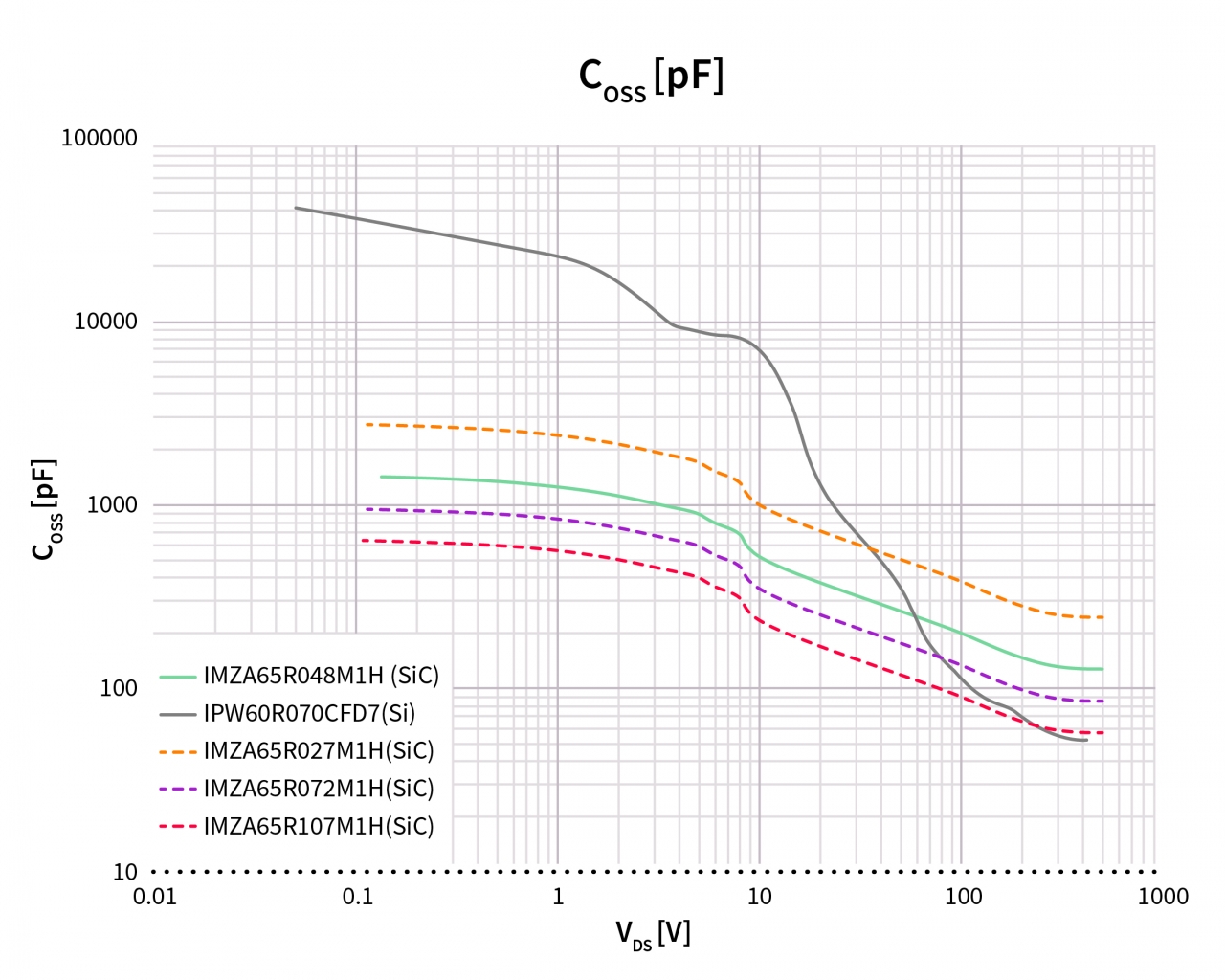

MOSFET에서 또 하나의 중요한 요소는 출력 커패시턴스 COSS다. 제로 전압이 아닌 턴온 시 이 에너지 EOSS를 소산시켜야 한다. 커패시턴스가 낮으면 높은 스위칭 속도를 사용할 수 있으나 턴온 시 드레인-소스(VDS) 오버슈트를 일으킨다.

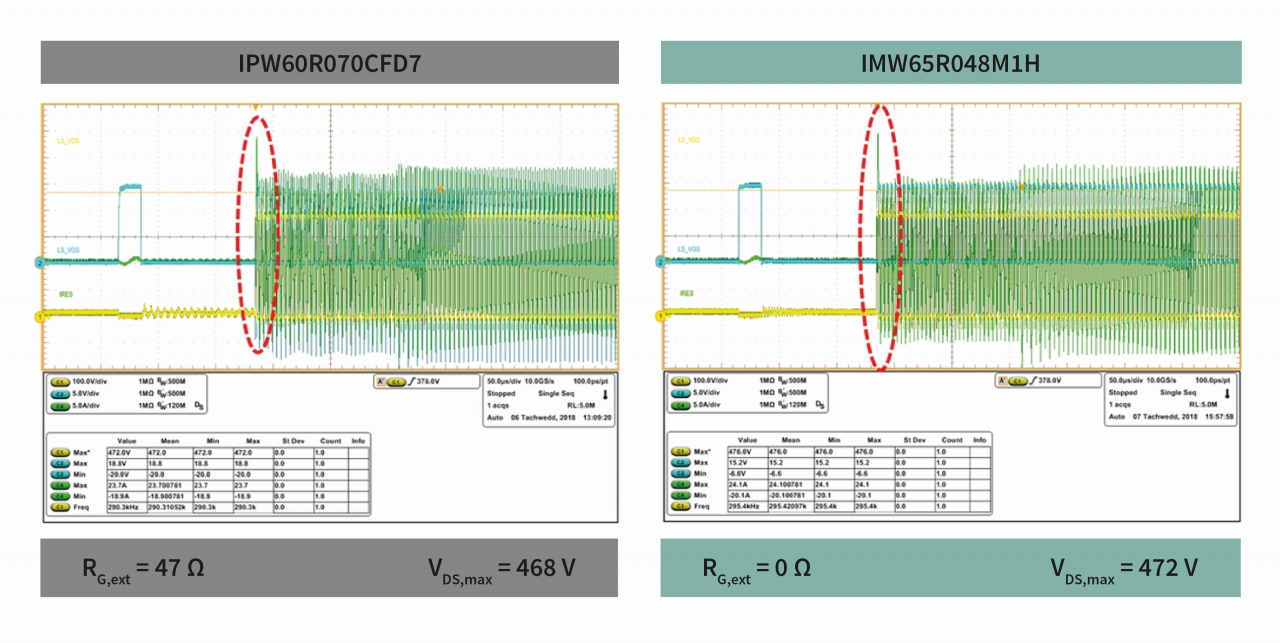

CoolMOS 스위치를 사용할 때 이 문제를 극복하기 위해서는 게이트로 저항(RG)을 사용해 스위칭 속도를 낮춰야 한다. 이렇게 하면 드레인-소스로 요구되는 80% 디레이팅(De-rating) 달성에 도움 된다. 대신, RG를 삽입하면 전류가 증가해 특히 턴오프 시 스위칭 손실을 늘린다는 단점이 따른다.

VDS 값은 대략 50~60V 지점부터, CoolSiC 디바이스가 동급 CoolMOS 디바이스보다 COSS가 높으나 COSS와 VDS의 관계는 훨씬 더 선형적이다[그림 4]. 그러므로 동일한 회로를 사용해 CoolSiC 스위치는 낮은 값의 외부적 RG 저항을 통해 요구되는 80% 디레이팅을 달성할 수 있다. 이는 공진 LLC DC/DC 컨버터와 같은 스위칭 토폴로지에 유용하다[그림 5].

SiC 기술이 장점만 있는 것은 아니다. 단순히 Si MOSFET을 SiC 디바이스로 교체하기만 해서 더 우수한 SMPS 성능과 효율을 달성할 수는 없다.

SiC 디바이스는 바디 다이오드 순방향 전압이 훨씬 높으며, 때에 따라 동급 Si 디바이스 대비 4배 더 높을 수 있다. 그러므로 단순히 Si를 SiC로 교체하기만 한다면 바디 다이오드 전도 손실이 4배까지 높아질 수 있다. 이는 경부하 조건으로 잠재적인 0.5%의 효율 향상 기회를 놓치는 셈이다.

그러므로 최대의 효율을 달성하기 위해서는 바디 다이오드가 아닌 채널을 통해 부스트 해야 한다. 또한 SiC MOSFET의 이점을 최대한 활용할 수 있도록 데드 타임을 조정하고 최적화해야 한다.

결론

650V SiC MOSFET 제품이 추가됨에 따라 더 다양한 애플리케이션에 SiC 기술을 활용할 수 있게 됐다. 97% 이상의 효율을 달성하고자 하는 시스템, 하드 정류가 발생할 수 있는 컨버터, 고전력 애플리케이션이 그 예다.

설계자는 SiC와 Si MOSFET의 특성이 다름을 이해해야 한다. 기존의 많은 SMPS 디자인은 곧바로 교체할 수 있겠지만, 최종 제품에서 SiC의 이점을 최대한 발휘하기 위해서는 게이트 구동 전압, 데드 타임 구현과 같은 회로의 특정 측면들을 조정하는 작업이 필요할 수 있다.

글: 르네 멘테(René Mente) 인피니언 시니어 애플리케이션 엔지니어

자료제공: 인피니언 테크놀로지스

- 이 글은 테크월드가 발행하는 월간 <EPNC 電子部品> 2020년 8월 호에 게재된 기사입니다.

그래도 삭제하시겠습니까?