기술 선두권 경쟁과 철옹성 같은 진입장벽

[테크월드=선연수 기자]

TSMC와 삼성전자를 필두로 초미세공정 기술은 끝을 모르는 미시세계로 들어서고 있다. 특히, 빅데이터를 처리하는 인공지능을 자동차, 홈 가전, 스마트폰 등 곳곳에 적용하기 위해서는 소형의 고도화된 시스템 반도체 기술력이 요구된다. 지난 2017년 2월 삼성전자가 10나노급 D램 개발에 성공하며 마의 벽 같았던 20nm의 한계를 깼고, 이젠 7nm에 이어 5nm, 심지어 2nm까지 바라보고 있다.

10nm 미만 진입은 선택 아닌 필수

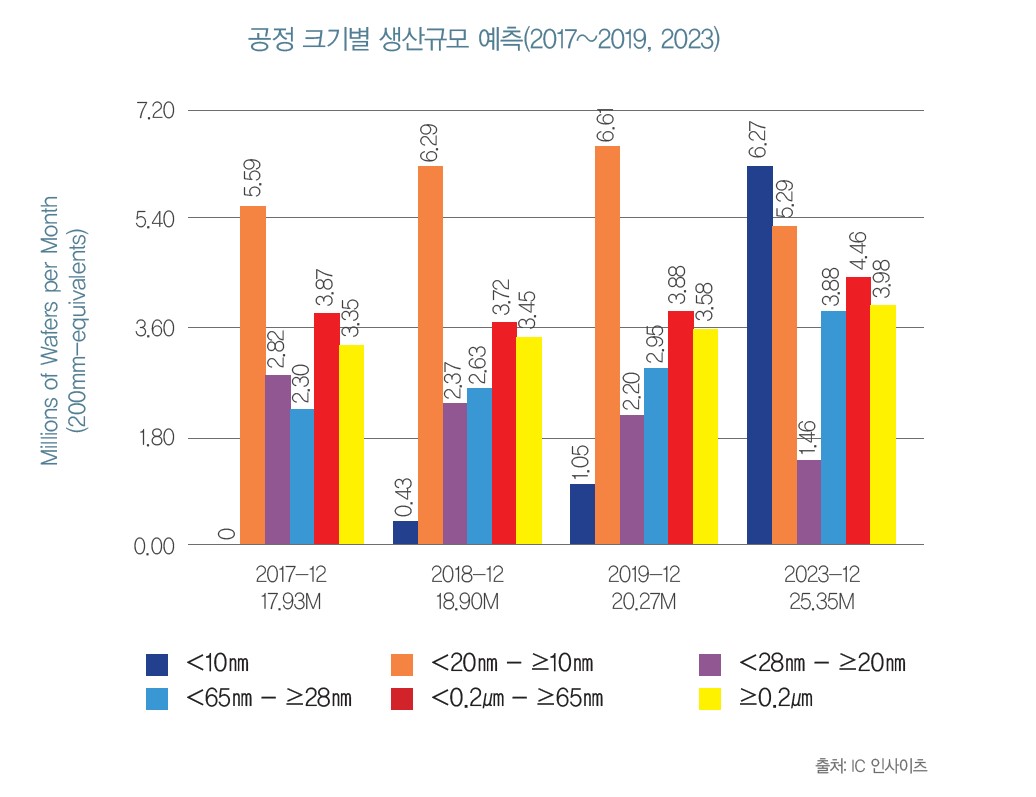

지난 16일(미국 현지시간) IC 인사이츠(IC Insights)에 의하면 10nm 미만 미세공정의 생산 규모는 지난해 웨이퍼 기준으로 43만 장을 기록했으며, 올해 2배 증가한 월 105만 장을 달성하고, 2023년에는 약 3배 성장한 월 627만 장으로 늘어날 것으로 전망된다. 또한, 2023년에는 10nm가 전체 미세공정 생산량의 25%를 차지할 것이란 예측이다. 현재 주류를 이루는 10~20nm 공정의 생산 규모는 올해 월 661만 장에서 2023년 529만 장으로 감소할 것으로 예상했다. IC 인사이츠는 삼성전자와 TSMC가 7nm 파운드리 양산 체제를 본격적으로 갖춤으로써 시장의 성장세가 두드러지고 있다고 분석했다.

현재 EUV 노광공정 장비를 유일하게 공급하는 ASML은 올 3분기 영업이익으로 약 8236억 원(6억 2700만 유로), 매출로 약 4조 원(30억 유로)을 달성했다. 이는 전년 동기 대비 7.6% 증가한 수치이며, 매출 총이익률은 43.7%를 나타냈다. 기존에 ASML은 올해 EUV 장비 생산 대수를 26대로 정했고, 이번 분기에만 23대의 장비를 수주받았다고 밝혔다. 이를 통해 얻은 예약 매출은 약 6조 5000억 원(51억 유로)에 달한다. 다가오는 2020년에는 35대의 EUV 장비를 생산할 예정이다.

EUV를 통한 초미세공정 기술은 ‘EUV 노광’, ‘초미세공정’ 모두 초고난이도의 기술력을 요구한다. 그러나 삼성전자와 TSMC 두 선두업체, 그리고 유일한 장비 공급업체 ASML만으로도 시장이 고성장세를 보이는 것은 초미세공정에 필수적인 미래 기술임을 증명한다. 반도체가 더욱 집적화되고, 고기능을 요구함에 따라 전력 소비량, 생산성, 기능성 측면에서 훨씬 유리한 초미세공정 반도체를 만들어 내야하고, 현재로선 EUV 기술을 적용할 수 있는 공정 기술을 획득해 진입 장벽을 부수는 것이 기업들에게 다음 세대로 넘어가는 큰 관문이 될 것이다.

GAA로 3nm 영역 넘보는 삼성전자

삼성전자는 2018년 하반기 7nm 공정 기술을 개발하고, 지난 4월 7nm 파운드리 제품을 출하했다. 같은 달에 5nm 공정 개발 또한 성공했으며, 올 하반기 6nm 제품을, 내년 초 5nm 제품을 양산할 계획이라고 밝혔다. 현재 EUV가 아닌 GAA(Gate-All-Around) 기술로 3nm 제품 개발을 진행하고 있으며, GAA 공정 설계 키트를 팹리스 고객에게 배포하는 방식으로 초미세 회로 기술에 투자하고 있다.

삼성은 GAA 기술을 1세대 3GAE(3nm Gate-All-Around Early), 2세대 3GAP(3nm Gate-All-Around Plus)로 분류한다. GAA는 전류가 흐르는 원통 채널 전면을 게이트가 둘러싸, 전류를 더 세밀하게 제어할 수 있다. 이를 통해 3GAE 공정의 경우 7nm 핀펫(FinFET) 대비 소비전력 50%, 칩 면적 45%의 감소 효과와 35%의 성능 향상을 이뤄낼 수 있다고 설명했다. 그러나 이 GAA는 가늘고 긴 나노와이어 형태로 전류가 흐르는 채널의 폭이 넓지 않아 충분한 전류를 확보하기 힘들다. 이를 위해 삼성전자는 나노와이어를 얇은 종이인 나노시트로 제작해 채널과 게이트 간 접촉 면적을 늘리는 MBCFET(Multi-Bridge Channel Field Effect Transistor) 기술을 개발했다.

지난 2월부터 삼성전자는 파운드리 생산시설인 화성 캠퍼스에 EUV 전용 라인을 추가 신설해 2020년부터 본격 가동할 계획이다.

공급처 확보가 관건, TSMC

TSMC는 2018년 EUV 기술이 적용되지 않은 N7 기술에 바탕한 7nm 제품 양산에 성공했다. 이를 통해 애플, 화웨이와 같은 글로벌 고객층을 빠르게 선점해 고객사의 스마트폰에 해당 기술을 적용한 칩을 공급했다. 이후 EUV 공정을 도입한 N7+ 기술로 7nm를 생산하고 있으나 아직 이 기술이 적용된 제품은 없는 상황이다. EE타임즈의 보도에 따르면, 린리 그룹(The Linley Group)의 린리 그웬냅(Linley Gwennap) 사장 겸 수석 분석가는 “현재 TSMC의 7nm 기술의 수율은 높으나, 삼성전자의 갤럭시 노트 10처럼 공급이 확정된 제품이 없다. 삼성전자가 기술 공급에 따른 수요처가 즉각 형성되는 것과는 대조적인 상황”이라고 분석했다. TSMC는 애플, 화웨이, AMD 측에 기술을 공급하고 있으며, 향후 이 업체들의 제품에 적용될 것으로 예상된다.

이 다음 기술로는 더 많은 레이어층을 쌓는 N6 기술, 5nm 제품을 제작하는 N5 기술, N5에서 더 나아가 성능은 높이고 전력 소모량을 낮춘 N5P, 3nm 공정을 위한 N3 기술을 개발 중에 있다. TSMC는 5nm 제품을 내년 초 양산할 것으로 업계는 예상하고 있으며, 3nm 구현에서는 삼성전자와 같이 새로운 기술이 도입될 것으로 보이며 이는 2022년 양산을 목표로 두고 있다. 또한, 중국 현지 언론에 의하면 TSMC가 대만 신주 과학기술단지에 공장을 건설하고, 2024년 가동을 목표로 2nm 공정 기술에 투자하고 있다고 보도했다.

10nm서 전전긍긍 인텔, 시기 노리는 SK하이닉스

반도체 업계에 의하면, 인텔은 지난 8월부터 EUV 장비를 구매하기 시작했으나, 실질적인 생산 시기를 3년 후로 연기한 것으로 알려져 있다. 초미세 경쟁 붐과 함께 인텔은 EUV 도입을 통한 7nm 제품 구현 계획을 꾸준히 소개해왔으나 여전히 10nm 미만 제품을 만들어내지 못하고 있다. SK하이닉스의 경우, EUV 장비는 보유하고 있으나 역시 실제 공정 시작 시기를 2021년 이후로 예측하고 있다.

- 이 글은 테크월드가 발행하는 월간 <EPNC 電子部品> 2019년 11월 호에 게재된 기사입니다.

그래도 삭제하시겠습니까?