0.1㎚급 공정에 적용… 리본펫, 파워비아 기술도 활용

반도체 공정 명칭에서 ‘나노미터’ 제거

인텔 파운드리 고객사로 퀄컴, AWS 유치

[테크월드뉴스=서유덕 기자] 인텔이 ASML과 협력해 차세대 초미세공정 장비인 High NA EUV를 공동 개발, 최초로 도입함으로써 2024년 0.1나노미터(㎚) 공정을 구현할 것이라고 27일 밝혔다.

이날 인텔 액셀러레이터 행사에서는 반도체 공정에 대한 새로운 명칭과 트랜지스터 혁신 기술 ‘리본펫, 파워비아’ 및 패키징 기술 ‘이밉(EMIB), 포베로스’가 소개됐으며, 인텔 파운드리 서비스의 첫 고객사로 퀄컴과 아마존웹서비스(AWS)가 공개됐다.

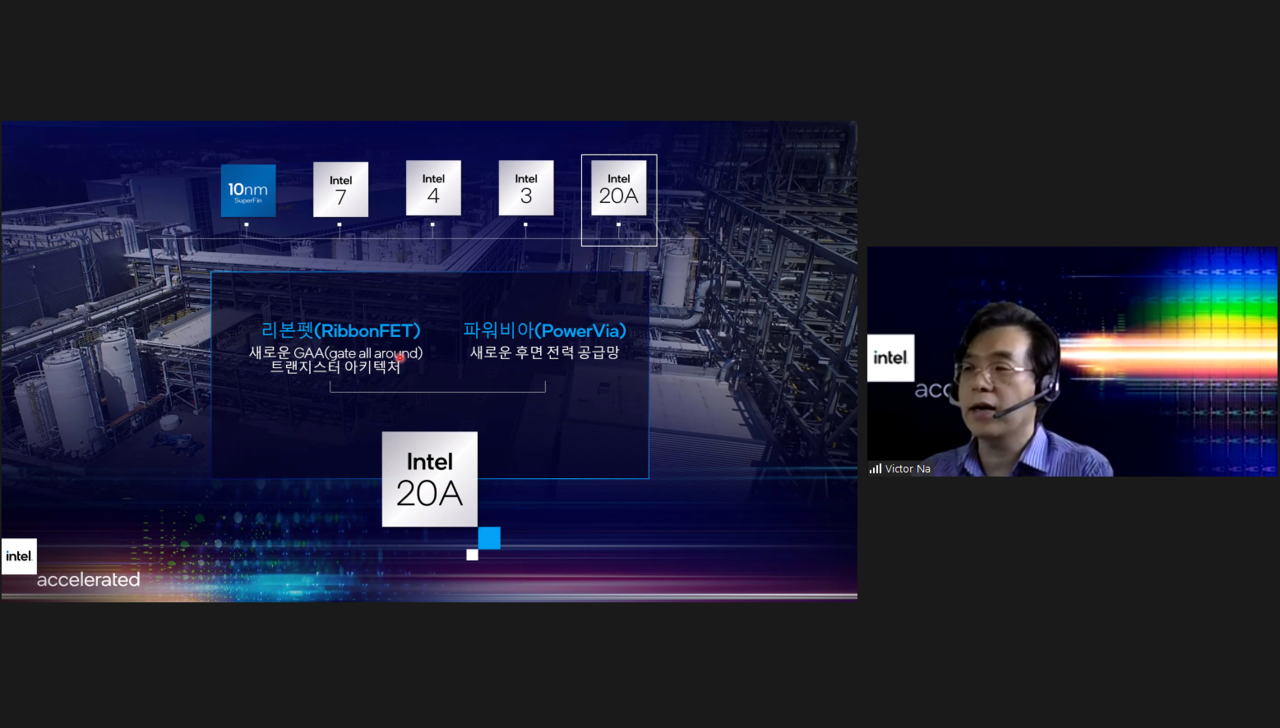

인텔은 2024년 이후 0.1㎚ 공정에서 제품을 생산할 계획이며, 이를 위해 ‘리본펫’, ‘파워비아’, ‘차세대 EUV’ 기술을 도입한다. 2011년 핀펫을 발표한 이후 선보이는 새 기술 ‘리본펫’은 GAA(Gate-all-around) 트랜지스터 아키텍처로, 더 빠른 트랜지스터 스위칭 속도를 제공하는 동시에 더 작은 면적 구현이 가능하며 다중 핀과 구동 전류가 동일하다. ‘파워비아’는 업계 최초로 후면 전력 공급을 구현한 인텔의 기술로, 웨이퍼 전면에 전력 라우팅이 필요하지 않아 신호 전송을 최적화한다. 아울러, 인텔은 ASML과 차세대 EUV 기술 ‘High NA EUV’ 개발을 위해 협력 중이며, 업계 최초로 해당 장비를 제공받을 계획이다.

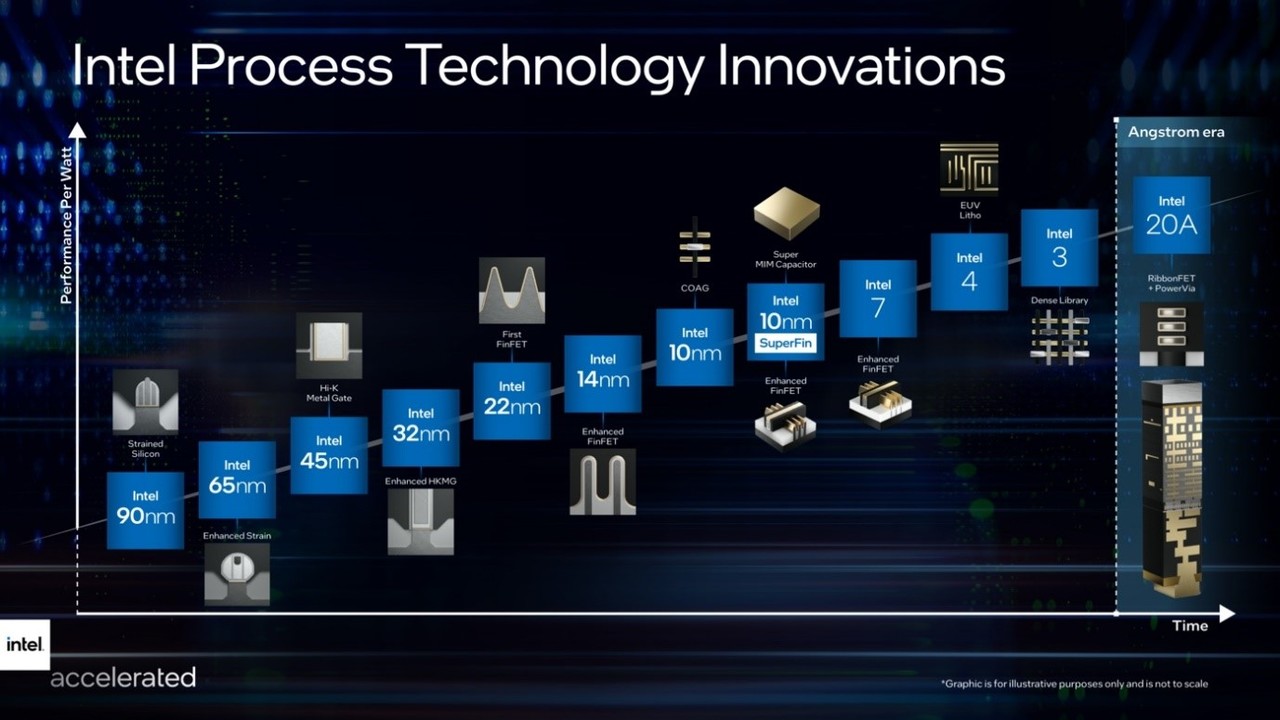

인텔은 공정에 대한 이해를 돕기 위해 트랜지스터의 게이트 길이를 기준으로 하는 명명 방식에서 탈피한 새로운 노드 이름을 사용한다. 각 노드명과 이를 뒷받침하는 기술은 다음과 같다.

▲ ‘인텔 7’은 기존 인핸스드 슈퍼핀이라고 불린 공정으로, 핀펫(FinFET) 트랜지스터 최적화를 기반으로 인텔 10㎚ 슈퍼핀(SuperFin)에 비해 와트당 성능을 약 10%~15% 향상시킨다. 인텔 7기반 제품은 2021년 선보일 클라이언트 PC용 ‘앨더 레이크(Alder Lake)’와 2022년 1분기 생산 예정인 데이터센터용 ‘사파이어 래피즈(Sapphire Rapids)’ 등이 포함될 예정이다.

▲ ‘인텔 4’는 7㎚ 공정에 해당하며, EUV를 도입해 면적을 개선하고 와트당 성능을 약 20% 향상한다. 클라이언트 PC용 ‘메테오 레이크(Meteor Lake)’, 데이터센터용 ‘그래나이트 래피즈(Granite Rapids)’를 포함 2023년 제품 출하를 위해 2022년 하반기에는 생산에 들어갈 예정이다.

▲ ‘인텔 3’은 추가적인 핀펫(FinFET) 최적화와 EUV 활용을 높여 인텔 4에 비해 와트당 성능을 약 18% 향상하고 추가적으로 면적도 개선한다. 인텔3 공정 기반 제품 생산은 2023년 하반기부터 시작한다.

▲ ‘인텔 20A’는 옹스트롬(0.1㎚)급 공정으로, ‘리본펫’과 ‘파워비아’ 기술을 활용한다. 2024년에 생산에 들어갈 것으로 예상된다.

▲ 향상된 리본펫 기반의 ‘인텔 18A’는 2025년 초를 목표로 개발 중이다.

패키징 로드맵과 각 단계별 제품은 다음과 같다.

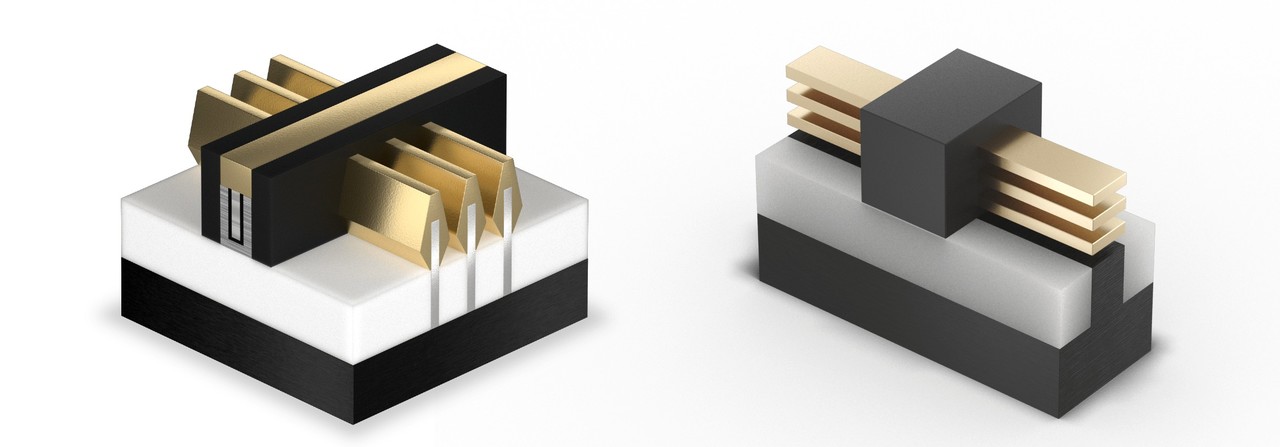

▲ 임베디드 멀티다이 인터커넥트 브릿지(EMIB)는 2.5D 임베디드 브릿지 솔루션으로 2017년부터 관련 제품이 출하되고 있다. 제온 데이터센터 제품인 사파이어 래피즈에 EMIB이 적용될 예정이며, 이는 모놀리식 설계와 거의 동일한 성능을 제공하는 듀얼 레티클 크기의 장치가 될 것이다. 사파이어 래피즈 이후 차세대 EMIB는 범프(bump) 피치를 55 마이크론에서 45마이크론, 나아가 40마이크론까지 개선할 예정이다.

▲ 포베로스(Foveros)는 웨이퍼 수준의 패키징 기능을 활용, 3D 적층 솔루션을 제공한다. 2세대 포베로스가 클라이언트용 제품인 메테오 레이크에 적용되며, 해당 제품은 36 마이크론 범프 피치, 여러 공정 기술로 만든 타일, 5~125W의 열 설계 전력 범위를 제공할 것이다.

▲ 포베로스 옴니(Foveros Omni)는 실리콘 다이를 서로 연결하고 모듈 설계를 위한 3D 적층 기술을 활용해 무한한 유연성과 성능을 제공하는 차세대 포베로스 기술이다. 포베로스 옴니는 여러종류의 공정으로 생산된 상부 다이와 기본 타일을 혼용해 다이 분리가 가능하며, 2023년에 대량 생산 가능할 것으로 예상한다.

▲ 포베로스 다이렉트(Foveros Direct)는 낮은 저항으로 구리와 구리를 서로 직접 연결할 수 있으며, 웨이퍼와 패키징의 경계를 모호하게 한다. 3D 적층 상호연결 밀도를 10 마이크론 이하로 범프 피치를 구현해 이전에는 달성할 수 없었던 기능별로 다이를 분리할 수 있는 새로운 개념을 제시한다. 포베로스 다이렉트는 포베로스 옴니를 상호 보완하는 제품으로 2023년 준비될 예정이다.

이들 기술은 인텔 내부 생산 라인과 파운드리 서비스에 모두 적용될 예정이며, 인텔 파운드리 서비스의 첫 고객사인 퀄컴과 AWS에도 제공될 방침이다. 퀄컴은 인텔 20A 공정을, AWS는 패키징 로드맵을 각각 제공받는다.

한편 4년 내 5개 노드 등 계획의 지연 가능성에 대해 박민진 인텔코리아 홍보 담당 상무는 “이미 기술 검증이 일정 수준 이상 완료됐으며, 2024년 이후에 나오는 인텔 18A에 대한 개발도 시작된 상태”라며 “파트너사의 참여 또한 인텔 기술에 대한 확신의 방증”이라고 일각의 우려를 일축했다.

나승주 인텔코리아 데이터센터 비즈니스 총괄 상무는 “면적과 게이트웨이 길이를 줄이는 개념을 넘어 소재와 재료, 구조 등을 변경함으로써 무어의 법칙이 지속될 수 있도록 할 것”이라고 언급했다.

그래도 삭제하시겠습니까?