[테크월드뉴스=이혜진 기자] 싱글톤이나 고조파(합성 전자파의 일종)를 감지하는 것은 고도의 연산 처리 능력을 필요로 한다. 이때 설계자는 프로그래머블 반도체(FPGA, 용도 변경이 가능한 반도체) 기판을 사용해 신호 생성 및 톤 감지에 대한 다양한 접근 방식을 평가할 수 있다.

프로그래머블 반도체를 써야 하는 이유

엔지니어는 때때로 개념 증명 시스템을 빠르게 구현해야 한다. 응용 프로그램에 맞는 평가 키트와 모듈을 늘 사용할 수도 없다. 이산 수학(전산학의 기초가 되는 수학)과 높은 연산처리 능력이 동시에 필요한 경우 특히 그렇다. 이때 FPGA 기판이 도움이 될 수 있다.

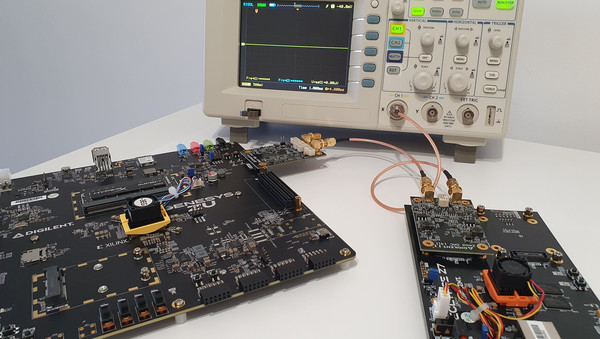

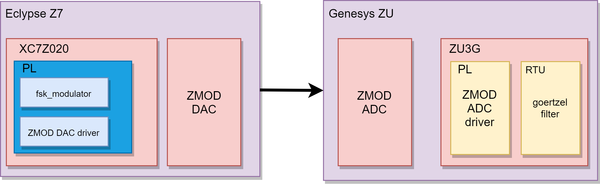

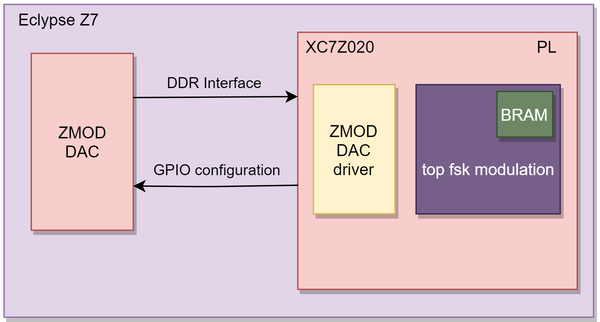

아날로그 신호로 연결된 2개의 FPGA 기판을 사용하면 쉽게 수행할 수 있다. 싱글톤을 생성하는 기판의 경우, 자일링스의 ‘징크-7000’ 올 프로그래머블 시스템 온 칩(SoC, 중앙처리장치나 메모리 등을 칩 하나에 전부 얹은 것)이 적용된 기판인 디질런트의 ‘이클립스 Z7’과 디지털-아날로그 변환기(DAC) ‘지모드 1411’을 사용할 수 있다. 이클립스에서 실행되는 신호 발생기(주파수 등 다양한 설정을 전환할 수 있는 기기)는 통신 시스템에서 흔히 볼 수 있는 주파수 편이 변조(디지털 신호를 아날로그 전송로를 통해 전송할 때 사용하는 주파수 변조 방식)로 신호를 생성한다.

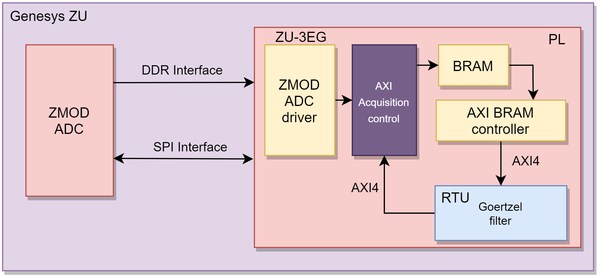

신호를 수신할 땐 자일링스의 ‘징크 울트라스케일+’ 멀티 프로세싱 SoC 기판이 적용된 플랫폼인 디질런트의 ‘제네시스 ZU-3EG’와 아날로그-디지털 변환기(ADC)를 활용할 수 있다. 제네시스의 온보드 멀티 프로세서 시스템온칩(MPSoC)은 쿼드 코어 Arm 코텍스-A53을 지원한다. 또 무선 처리 장치(RPU)인 듀얼 코어 Arm 코텍스-R5F와 복수의 프로그래밍 언어(PL)가 포함돼 있다.

주파수 편이 방식 변조로 톤 생성 구현

주파수 편이 방식 변조(FSK∙Frequency Shift Keying) 기술은 높은 반송 주파수를 다른 주파수로 조절해 입력 데이터(0 또는 1)의 정보를 누적한다. 그런 다음 주파수 수신기가 수학적 기법인 ‘고속 푸리에 변환(FFT)’과 ‘이산 푸리에 변환(DFT)’ 또는 이를 평가하는 디지털 신호 처리 기술인 ‘괴첼 필터’로 생성된 아날로그 신호를 복원한다.

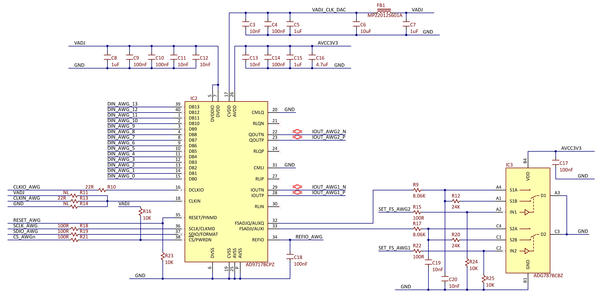

출력 신호에 요구된 높은 주파수를 달성하려면 빠른 클럭 신호(중앙처리장치가 특정 주기로 주어지는 신호에 맞춰 연산하는 것)가 빨라야 한다. 이클립스 기판에는 징크 APSoC에 연결된 2개의 클럭 소스가 있다. 하나는 처리 서브시스템(PS)에 직접 연결돼 있고, 다른 하나는 PHY(Physical Layer) 칩을 사용한 이더넷(근거리 통신의 표준 규격)에서, 또 다른 하나는 PL에서 나온다. 변조된 신호를 생성하기 위해 PS가 필요하지 않기 때문에, 25메가헤르츠(MHz∙100만헤르츠)의 주파수로 작동하는 PL에 연결된 클럭을 사용할 수 있다. 더 높은 주파수를 달성하기 위해, 예를 들어 100MHz, 혼합 모드 클럭 관리자(MMCM) 중 하나를 활용할 수 있다.

FSK용 반송 신호는 SoC의 블록 랜덤 액세스 메모리(BRAM∙FPGA에 많은 양의 데이터를 저장하는 메모리) 중 하나에 사인파(주기적, 연속적으로 진동하는 파동)로 저장된다. 클럭의 모든 엣지에서 BRAM의 주소로부터 값을 읽고 주소가 증분된다.

변조된 신호를 아날로그 도메인으로 변환하기 전에 지모드 DAC 모듈의 디지털-아날로그 변환기를 구성해야 한다. 이는 기판에 아날로그 신호를 전달하는 장치의 집적회로(IC∙Intergrated Circuit)을 필요한 값으로 설정한다.

괴첼 알고리즘을 이용한 싱글톤 감지

아날로그 신호는 제네시스 ZU에 장착된 지모드 ADC 모듈의 아날로그-디지털 변환기에 의해 획득된다. 해당 기판은 아날로그 장치에서 아날로그-디지털 변환기인 AD9648을 사용한다. 채널은 2개, 해상도는 14비트다. 기판을 구성하고 기동할 땐 전원 공급 장치를 사용하도록 설정해야 한다. 디질런트에서 만든 모듈은 이런 작업을 처리한다. 지모드는 데이터 전송을 위해 SPI(Stateful Packtet Inspection) 기반의 포트와 D램(DDR) 인터페이스로 입출력 장치(I/O)의 규격 중 하나인 SYZYGY에 순응하는 인터페이스를 통해 제네시스 ZU 기판에 연결한다.

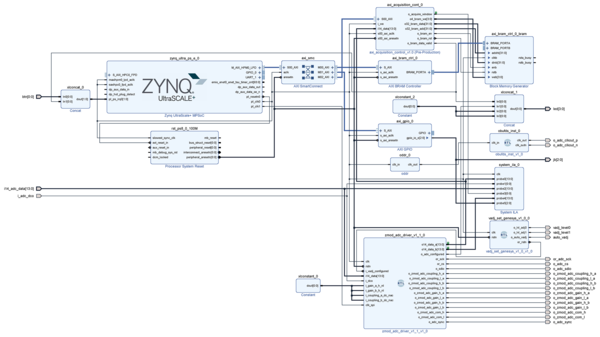

징크 울트라스케일+ 장치에서DDR 인터페이스를 만들려면 자일링스의 데이터 입력용 레지스터(중앙처리장치에 들어있는 소규모 데이터 기억 장치)인 ‘IDDRE1’의 기본 요소를 사용해야 한다. 이런 기본 요소는 자일링스 7 시리즈 FPGA의 IDDR 기본 요소와 유사하다. 하지만 새로운 버전과는 호환되지 않는다. 통신을 가능하게 하기 위해 PS는 2개의 클럭 신호를 생성해야 한다. 하나는 50MHz의 SPI 포트를 통한 전송을 위한 것이다. 다른 하나는 DDR 인터페이스 및 제어용 AXI(Advanced Extensible Interface) 모듈 및 100MHz의 BRAM에 대한 것이다.

모든 샘플을 읽고 BRAM으로 이동하면 괴첼 알고리즘이 실행돼 해당 주파수가 신호에 있는지 감지한다. FFT를 사용해도 싱글톤의 존재를 발견할 수 있지만, 복잡한 숫자의 곱셈을 수 차례 실행해야 해 비효율적이다. 이 때 DFT를 채택하면 곱셈 수가 줄어든다. 그러나 여전히 복잡한 숫자에 대한 연산 문제를 해결하지는 못한다.

반면 괴첼 알고리즘은 계산 횟수를 줄여 효율적이다. 제네시스 ZU 기판에서 알고리즘은 온보드 징크 MPSoC의 Arm 코텍스-R5F에서 실행될 것이다.

필터는 선택한 톤을 계산하기 위해 정적 샘플 수가 필요하다. 해당 샘플은 PL과 PS 사이에서 공유돼야 한다. 디질런트에선 BRAM에 쓰는 AXI IP 블록을 사용할 것을 제안한다. 이 BRAM은 듀얼포트로 연결된다. 하나는 AXI 수집 제어 모듈에, 다른 하나는 AXI BRAM 컨트롤러에 연결된다. AXI 제어 모듈은 2개의 레지스터를 포함한다.

다음 그림은 징크 울트라스케일+ 블록, 지모드 ADC의 드라이버, 수집 제어 모듈, BRAM, 샘플을 저장하기 위한 AXI BRAM 컨트롤러 및 기타 AXI 블록을 포함한 복원 시스템에 대한 제네시스 ZU 기판의 블록 다이어그램을 나타낸다.

‘징크 울트라스케일+’ 사용하면 속도 개선 가능

괴첼 알고리즘은 RPU 덕분에 징크 울트라스케일+ 장치에서 잘 작동한다. 하지만 엣지에서 사용하기에 부적합하다. RPU가 500MHz에서 실행되더라도 최대 주파수는 16킬로헤르츠(kHz∙1kHz=1000Hz)로 제한된다.

알고리즘의 성능을 향상시키기 위한 옵션은 다음과 같다. 불필요한 주파수의 성분을 제거할 때 쓰는 노치 필터를 사용하면 계산에 필요한 시간을 괴첼 알고리즘에 필요한 시간의 일부로 줄일 수 있다. 그러나 이 경우 일부 정보가 손실된다.

또 다른 옵션은 징크 울트라스케일+에서 RTU의 연산을 담당하는 부품을 모두 사용하는 것이다. 시간을 줄일 수 있는 DFT와 달리, 무한 임펄스 응답 필터(IIR)는 다음을 연산하기 위해 이전 출력을 필요로 한다. 이때 출력이 주파수의 2배로 업데이트되기 때문에 처리량이 향상된다.

FPGA로 싱글톤을 감지하는 프로젝트에 대한 세부 정보는 핵스터(Hackster) 홈페이지에서 확인할 수 있다.

자료 제공 : 디질런트

그래도 삭제하시겠습니까?