[테크월드=선연수 기자] 사물인터넷용 인공지능(AI)부터 임베디드 비전, 하드웨어 보안, 5G 통신, 산업 자동화, 자율주행차에 이르기까지 새롭게 떠오르는 애플리케이션은 네트워크 엣지에서 동작하는 제품을 설계하는 개발자들의 하드웨어 요구사항을 재정의하고 있다. 이런 애플리케이션을 지원하기 위해 엣지 디바이스에는 ▲저전력 소모 ▲고성능 ▲높은 신뢰성 ▲소형 폼팩터 등의 하드웨어 옵션이 요구된다.

래티스 반도체(이하 래티스)는 이런 특성의 하드웨어 플랫폼을 제공하기 위해 수년 전부터 FPGA 개발 공정에서 새로운 혁신을 찾아 나섰다. 연구는 래티스의 28nm FD-SOI(Fully Depleted Silicon-on-Insulator) 공정 기술 사용을 지원하는 저전력 FPGA 공급업체가 되기로 하면서 활발하게 진행됐다. 삼성전자가 개발한 이 공정은 오늘날 판매되는 반도체 제조에 대부분 사용되는 벌크 CMOS 공정 기술과 유사하지만, 디바이스 크기와 전력 소모를 더 높은 수준으로 줄이고 성능과 신뢰성도 개선한다.

래티스는 새로운 제조 플랫폼을 지원하면서 시스템 솔루션부터 FPGA 패브릭 아키텍처, 개별 회로에 이르는 기술을 지원한다. 이와 함께 래티스는 새로운 제조 공정과 혁신을 결합한 래티스 넥서스(Lattice Nexus) FPGA 개발 플랫폼을 선보였다.

저전력 FPGA의 새로운 기반, 래티스 넥서스

래티스 엔지니어에게 있어 FD-SOI 공정은 내재된 고유한 특성을 이용해 새로운 회로를 설계할 기회다. FD-SOI는 프로그래밍 가능한 바디 바이어스 지원을 통해 벌크 저항이 트랜지스터의 바디에 있어 개발자가 동작 중 트랜지스터의 강도를 제어할 수 있다. 래티스 R&D팀은 개발자가 설계의 특정 전력과 열 관리 요구에 따라 고성능 모드나 저전력 모드로 동작하도록 선택할 수 있는, 프로그래밍 가능 바디 바이어스를 개발했다. 개발자는 간단한 소프트웨어 스위치로 동작 모드를 제어할 수 있다.

고성능 또는 저전력 동작으로 바디 바이어스를 프로그래밍함으로써, 개발자는 애플리케이션의 전력 소모와 열 관리 요구를 최적화한 FPGA의 전력·성능을 달성할 수 있다[그림 1]. 이는 배터리로 동작하는 엣지 디바이스의 전력을 절약하고, 산업·데이터센터 운영과 관련된 막대한 전기 비용 절감에 영향을 준다. 래티스는 넥서스 플랫폼으로 제조된 FPGA의 경우, 동급 경쟁 FPGA보다 최대 75% 낮은 전력 소모를 제공한다고 추산했다.

메모리 늘려 AI 프로세싱 가속화

디바이스 개발자는 네트워크 엣지에서 AI와 같은 새로운 기술을 지원하려면 시스템을 더 스마트하게 만들어야 한다. 엣지 디바이스가 엣지에서 실시간 데이터 처리와 분석을 수행할 수 있도록 시스템에 더 많은 인텔리전스 기능을 통합하고 이를 실현할 필요가 있다.

AI 설계자는 AI 추론 알고리즘이 매우 계산 집약적이기에 계산을 위한 값을 국지적으로 저장하는 대형 메모리 블록이 필요하다. 지금까지는 알고리즘 구현에 높은 수준의 DSP가 필요할 때, 칩을 떠나 시스템의 또 다른 프로세서나 클라우드로 이동했다. 이와 같이 AI 계산을 오프 칩으로 수행할 경우, 고객의 데이터를 클라우드로 전송하면서 데이터 개인정보 보호·보안과 관련된 우려가 높아질뿐더러 데이터 지연 문제까지 발생한다.

래티스는 넥서스 FPGA 플랫폼에서 데이터를 국지적으로 저장·계산할 수 있도록 더 큰 RAM 블록을 통합하고, DSP 블록을 최적화해 지연 문제를 해결한다. 넥서스 FPGA는 이전 래티스 FPGA보다 절반의 전력 소비로 2배 높은 성능을 제공한다. 이를 통해 구현한 로컬 엣지 AI 추론은 산업용 자율 로봇, ADAS 시스템, 보안 카메라, 스마트 도어벨 등 적용 분야가 다양하다.

기존 대비 소프트 에러율 100배 개선

일반적인 반도체 디바이스는 디바이스의 트랜지스터에 부딪히는 고에너지 입자(일반적으로 우주선 또는 알파 입자)에 의해 부정적인 영향을 받을 수 있다. 이 현상을 소프트 에러라고 부른다. 이 에러로부터 시스템을 복구하기 위해서는 FPGA가 자체적으로 리셋해야 하지만, 시스템 다운 타임이 수 밀리초조차도 허용되지 않는 미션 크리티컬한 애플리케이션에서는 채택하기 어려운 선택지다.

이를 막기 위해 래티스의 벌크 CMOS 반도체 제조 공정으로 개발된 디바이스는 주로 온칩 소프트 에러 정정(SEC), 에러 코드 정정(ECC) 블록 등 소프트 에러를 완화하는 기능을 포함하고 있다. 넥서스 FPGA는 SEC, ECC 지원과 함께 FD-SOI 제조 기술의 일부인 박막 산화막 층에 의해 입자가 기판에 부딪히는 영향으로부터 FPGA의 모든 트랜지스터를 보호한다.

그 결과 넥서스 플랫폼으로 개발된 FPGA는 다른 FPGA 대비 100배 개선된 소프트 에러율을 나타낸다. 특히, 디바이스 고장이 중대한 손상, 재산 피해와 직결되는 자동차나 산업용 기기 등의 미션 크리티컬한 영역에서 우수한 신뢰성이 중요한 특성으로 작용한다.

로직 밀도는 그대로, 풋프린트는 1/10로

넥서스 플랫폼은 엣지 디바이스에 요구되는 작은 폼팩터에 대한 사항도 만족한다. 일반적으로 데이터센터의 데이터 분석 애플리케이션 제품 설계 시, FPGA 업체들은 더 커지는 제품 아키텍처로 인해 소형 FPGA에는 일반적인 로직 셀 수에 맞춰 작업하기 어려워한다. 래티스는 그간 축적해온 전문지식을 바탕으로, 비슷한 로직 밀도 수준을 가진 경쟁 FPGA 대비 물리적 풋프린트가 10배 더 작은 디바이스를 구현할 수 있는 초소형 FPGA 아키텍처를 지원한다.

아키텍처부터 데모, SW까지

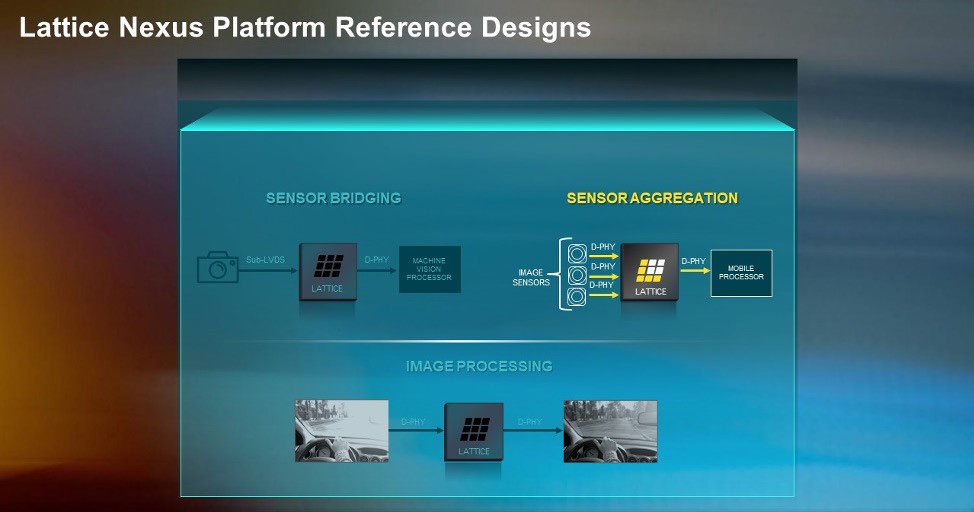

트랜지스터 아키텍처의 개발 외에도 고객이 설계상에서 넥서스 FPGA를 더 빠르고 쉽게 구현할 수 있도록 설계 공정에서 더 높은 수준의 추상화를 고려했다. 센서 병합, 센서 브리징, 이미지 프로세싱을 포함해 기존에 목표해온 통신, 컴퓨팅, 산업, 자동차, 소비자 분야에서 일반적인 애플리케이션을 구현할 수 있도록, 직관적인 설계 소프트웨어, 사전 제작된 소프트 IP 블록, 평가 보드, 키트, 레퍼런스 디자인을 제작, 소싱, 검증했다.

센서 병합 데모([그림 2]의 Sensor Aggregation 부분)는 고객이 제품을 신속하게 출시할 수 있도록 돕는다. 데모는 임베디드 비전 시스템에 사용되기 위해 최대 4개의 소스로부터 비디오 데이터 스트림을 가져온다. 이를 단일 스트림으로 결합한 후 고속 MIPI D-PHY를 통해 해당 스트림을 디스플레이나 프로세서로 전송해 추가적인 프로세싱을 수행한다.

데모는 여러 대의 카메라나 레이더 센서로부터 데이터를 수집하고 병합한 뒤, 이를 프로세서에 전달해 실시간으로 안전 결정을 내려야 하는 ADAS 시스템에도 활용할 수 있다. 이 경우, 개발자는 자동차 AP에 여러 개의 센서를 연결하지 않아도, 시스템의 PCB에서 트레이스 수를 줄이고 AP I/O 포트를 절약해 시스템 비용과 전체 크기를 절감할 수 있다.

소프트웨어 측면에서는 다양한 애플리케이션을 구현할 수 있도록 래티스 넥서스 FPGA는 설계 소프트웨어는 물론, 래티스가 선택한 사전 설계된 IP 라이브러리도 함께 제공한다.

넥서스 기반 첫 FPGA, 크로스링크-NX

오늘날 엣지 디바이스 시장은 초소형 풋프린트로 최소한의 전력만 소비하면서 더 높은 성능과 신뢰성을 제공하도록 요구받고 있다. 래티스는 오랜 역사를 통해 개발자가 다양한 애플리케이션을 위해 스마트한 저전력 엣지 디바이스를 출시할 수 있도록 돕는다.

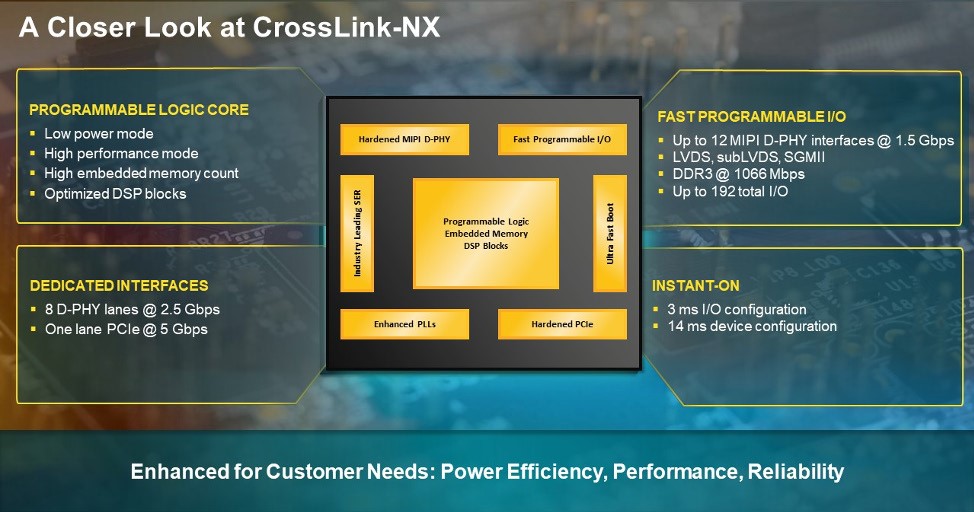

래티스 넥서스로 개발되는 4가지 제품군 중 첫 번째 디바이스인 크로스링크-NX(CrossLink-NX)는 크로스링크 FPGA(CrossLink FPGA) 제품군에 기반해, 비디오 신호 브리징, 분할, 병합을 위해 크로스링크로 지원하던 모든 비디오 신호 애플리케이션을 구현할 수 있다[그림 3].

크로스링크-NX는 기존 대비 2배 빠른 동작 속도, 더 높은 메모리 대 로직 비율, 최적화된 DSP, 더 큰 로직 용량, 더 빠른 I/O를 제공해 AI 알고리즘을 이용한 비디오 데이터 처리를 돕는다.

산업용, 자동차 분야에서는 기존 대비 최대 10배 작은 폼팩터로 소프트 에러율을 최대 100배까지 낮춰 신뢰성을 높였다. 래티스는 빠른 제품 개발을 위해 크로스링크-NX FPGA에 기반한 다이아몬드 2.0 FPGA(Diamond 2.0 FPGA) 개발 툴, 검증된 IP 블록, 애플리케이션 레퍼런스 디자인을 함께 지원한다.

자료제공: 래티스 반도체

- 이 글은 테크월드가 발행하는 월간 <EPNC 電子部品> 2020년 9월 호에 게재된 기사입니다.

그래도 삭제하시겠습니까?