[테크월드=선연수 기자]

최근 자율주행차의 상용화가 임박함에 따라 이를 뒷바침 해 줄 전자 제어에 대한 관심이 높아지고 있다. 특히 단순한 제어의 오류가 치명적인 결과를 초래할 수 있어 기존의 수준을 뛰어넘는 고품질의 반도체 집적 회로가 요구되고 있다. 대부분의 불량은 제품 출하 전 적절히 관리돼 실사용에 중대한 영향을 끼치진 않으나, 소프트 에러(Soft Error)의 경우 일회성 불량으로 불량 분석을 통한 원인 분석이 불가능한 경우가 대부분이다. 이로 인해 기존의 생산 관리로써의 한계를 갖게 된다. 이 글에서는 최고 수준의 안전 기준을 만족하기 위해 소프트 에러의 원인과 대처 방안에 대해 알아본다.

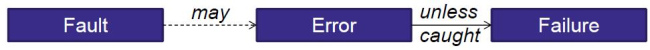

반도체 집적 회로 제품의 비정상적인 상태나 동작을 의미하는 폴트(Fault), 에러(Error), 페일러(Failure)는 용어적으로 가끔 혼용되지만 각기 다른 의미를 지닌다. 폴트는 에러를 발생할 수 있지만, 잠재적이거나 단순히 사라지기도 한다. 하드웨어에선 결함(Defect), 미비점(Imperfections), 외부 환경과의 상호작용으로 폴트가 발생할 수 있다. 폴트의 대표적인 예로는 반도체 집적 회로 제조 결함에 의한 발생, 우주선(Cosmic Ray)에 의한 비트 플립(Bit Flip)이 있다.

폴트는 대개 영구적인 폴트, 간혈적 폴트, 일시적인 폴트 3가지 경우로 나눠진다. 영구적인 폴트는 시정 조치(Corrective Action)가 취해지지 않는 한 영속적으로 존재하며, 예로는 트랜지스터의 이상 동작을 발생시키는 옥사이트(Oxide)층의 마모(Wear-out)가 있다. 간혈적 폴트는 발생, 소멸을 반복하며 영구적인 고장의 발생 가능성을 조기에 알려주기도 한다. 일시적인 폴트는 매주 짧은 시간 동안 존재하며, 대표적으로 우주선에 의한 중성자 입자와 실리콘의 충돌로 발생하는 경우다. 관련 자료에 따르면 반도체 집적 회로의 일시적 폴트는 다른 모든 고장을 전부 합친 값보다 훨씬 많은 70%의 비중을 차지한다. 반도체 집적 회로 제조 공정이 미세화되면서 각 노드의 정전 용량이 작아져 전하의 수가 감소함으로써, 입자 충돌로 인한 비트의 반전 확률이 증가하고 있다.

반도체 집적 회로에서 대부분의 폴트는 제조 공정의 변동으로 발생되며, 이는 출하 전 다양한 테스트 기법으로 적절히 관리할 수 있다. 그러므로 페일러의 대부분은 칩의 노화(Aging)나 방사선에 의한 에러와 관련된다. 노화에 대한 제품 불량 원인은 다양하게 연구됐으나, 방사선에 의한 동작 이상은 아직까지 많이 연구되지 않았으며 개선 방향 또한 미비한 수준이다. 그러나 최근 각광받는 자율주행 분야에서, 자동차 기능 안전성 국제표준 ISO26262의 자동차의 위험 등급 ASIL(Automotive Safety Integrity Level) 중 가장 엄격한 테스트 규제 등급인 D를 만족해야 하며, 이는 10FITs(Failure In Time, 10억 시간당 10번 고장)를 의미한다. 해당 기준을 만족하기 위해 소프트 에러에 대한 적극적인 대처가 필요하다.

메모리 폴트에서 하드 에러(Hard Error)는 반도체 집적 회로의 물리적 결함으로 인해 비트가 지속적인 에러를 일으키는 것이며, 소프트 에러는 일시적으로 비정상 비트의 값을 나타내는 것으로 분류할 수 있다. 비정상 비트의 값을 나타낼 경우 검출과 수정이 가능한 에러(DCE, Detectable Correctable Error), 검출은 가능하나 수정 불가능한 에러(DUE, Detectable Uncorrectable Error), 사이런트 데이터 변형(SDC, Silent Data Corruption) 총 3가지로 분류된다.

DCE는 하드웨어나 소프트웨어 에러 수정 기술을 통해 상위 레벨의 인식 없이도 관리할 수 있다. DUE는 코드 실행 중지를 발생시킬 수 있으며, SDC는 응용 프로그램 레벨의 이상 결과를 발생시켜 사용자가 이를 인지하지 못하는 상황이 일어날 수 있다.

이제 전체 반도체 집적 회로 고장의 70% 이상을 차지하는 일시적 고장의 주요 원인에 대해 알아보자.

알파 입자

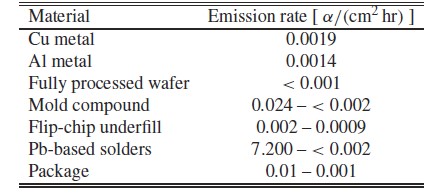

반도체 칩 내부로부터의 알파 입자는 웨이퍼, 패키지 재료, 솔더 등의 물질로 인해 발생된다. 알파 입자는 이중 이온화된 헬륨 원자(4He2+)로, 두 개의 양성자와 두 개의 중성자로 구성된다. 패키지 재료과 솔더 등은 방사성 동위원소를 포함해, 낮은 에너지로 붕괴될 경우 알파 입자를 발생시킨다. 발생된 알파 입자는 약 4~9MeV를 가진 채로 실리콘을 통과해 전자, 정공의 쌍을 발생시키며, 평균적으로 3.6eV의 운동에너지를 상실한다. 이는 수백만의 전자, 전공 쌍을 발생시키는 것을 의미한다. 알파 입자가 운동에너지를 상실함으로써 이동속도가 낮아지며, 이는 시간이 지날수록 전하 생성율이 증가하는 것을 의미한다.

반도체 집적 회로 패키지 내의 알파 입자 발생 원인을 최소화하기 위해, 방사선율이 최소 0.001α/cm2hr 이하인 물질을 사용해 패키지를 제조한다. 이를 통해 알파 입자의 발생을 효과적으로 방지할 수 있다.

우주선으로 인한 중성자 입자

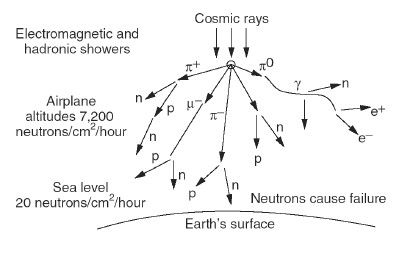

소프트 에러는 알파 입자 이외도 우주선으로부터 발생할 수 있으며, 은하계나 태양풍으로 인한 우주선이 주 요인이다. 우주선으로 인해 발생하는 입자의 경우, 양성자(89%), 알파 입자(10%), 중원자핵(1%)로 구성된다. 우주선은 지구 대기와의 상호 작용을 통해 복잡하고 연속적인 2차 입자들을 생성한다.

우주선에 의한 대부분의 전하들은 지구 자기장으로 인해 지표면까지 도달하지 못하지만, 우주선으로 생성된 약 1%의 중성자들은 지표면에 도달한다. 이때 약 5MeV 이상의 에너지를 가진 중성자는 소프트 에러를 발생시킬 수 있어, 우주선에 의한 소프트 에러의 확률은 중성자와의 상호 영향만으로도 충분히 예측 가능하다.

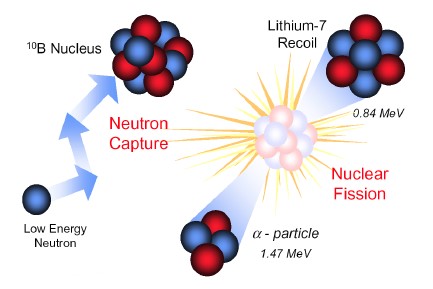

중성자로 인한 보론 핵분열

세 번째로 반도체에 영향을 주는 이온 입자의 발생은 보론 원자핵과 우주선 간의 작용에 따른다. 보론의 동위원소로 10B와 11B가 있으며, 10B 동위원소의 경우 중성자에 노출될 시 매우 불안정하다. 대부분의 동위원소는 중성자를 흡수할 때 감마 양성자만을 방출하나, 10B는 리튬-7 되튐핵과 알파 입자로 핵분열을 하게 된다. 리튬 되튐핵은 0.84MeV나 1.014MeV를 가지며, 방출된 알파 입자는 1.47MeV의 에너지를 가진다. 두 입자는 실리콘 회로에 전하를 생성시킬 수 있어, 소프트 에러가 발생한다.

이와 같은 보론은 반도체 제조 공정에서 p타입 불순물로 광범위하게 사용되며, BPSG(Boron Phosphor-Silicate Glass)층에 사용된다. SRAM은 중성자로 인한 보론의 핵분열이 소프트 에러의 주요 원인으로 밝혀지고 있고, 미세 공정이 진행될수록 보론으로 인한 영향이 증가하는 추세다.

소프트 에러의 물리적 분석

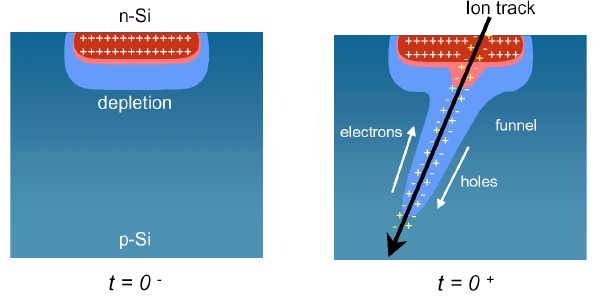

중성자 입자와의 충돌로 발생된 알파 입자와 리튬-7 되튐핵은 실리콘 회로에 영향을 주며, 이온화된 입자와 실리콘 원자 간의 쿨롱력에 의해 반도체 소자에 에너지를 전달한다. 이온화된 입자는 반도체 회로에 충돌해, 피코 단위의 시간 동안 전도성의 국부적인 전자, 전공 쌍의 컬럼을 생성한다. 이온화된 입자가 p-n 접합부에 도달하면 생성된 전자와 전공의 쌍이 공핍 영역의 전기장을 파괴해, 각각 양극과 음극 쪽으로 드리프트 한다. 이로 인해 기존 공핍 영역의 총 전하량과 전압차가 감소한다. [그림 4]는 알파 입자가 공핍 영역을 관통할 때, p-n 접합부에서 발생하는 전하 생성과 전자 전공의 흐름 방향을 보여준다.

[그림 4]와 같이 안정된 기판에서 이온의 진행 방향에 따라 전기장이 생성되고, 깔때기 효과(Funneling Effect)로 알려진 전하 집합 메커니즘이 생성된다.

깔때기 효과는 비교적 짧은 시간(2~3ps)내로 발생·소멸해, 순간적인 소모 전류의 급증을 일으킨다. 500ps 이내에 생성된 전하들은 서브 기판에 흡수·소멸되며, 이상이 발생한 전기장은 원래의 상태로 회복하고 p-n접합 또한 원래의 상태로 회복한다.

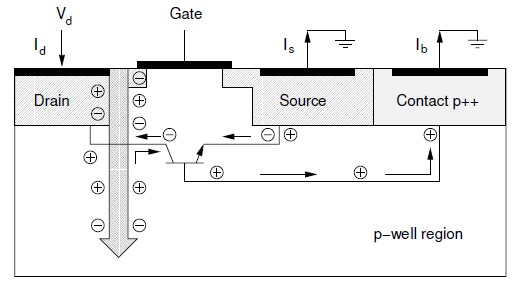

[그림 5]는 이온이 충돌한 후, 드레인 전류가 트랜지스터의 소스와 기판에 공유되는 현상을 나타낸다.

소프트 에러의 민감도를 낮추기 위해 여러 제조 단계에서 다음과 같은 방안을 적용한다. 반도체 집적 회로 제조에 대해 낮은 알파 입자를 방출하는 패키지와 웨이퍼 재료를 사용하며, 초고순도의 실리콘 공정 재료와 낮은 알파 입자를 방출하는 솔더 범프와 쉴딩 레이어(Shielding Layer)를 사용해야 한다.

설계 과정에서 중요 노드의 캐패시턴스 값을 증가시키거나, Pull-up 트랜지스터의 이득을 증가시키는 등의 설계 변경이 도움을 줄 수 있다. 또한, 부가회로를 넣어 올바른 회로 출력을 선택하는 방법도 있으며 예로는 TMR(Triple-Modular Redundancy) 설계 기법이 있다.

시스템 레벨에서 에러를 검출하고 복구할 수 있는 알고리즘을 통해 소프트 에러 발생에 대처할 수 있고, 이중 연산을 이용해 일치된 값의 출력 여부를 확인하는 방법 등이 있다.

결 론

현재 휴대폰이나 차량용 메모리 소자로 가장 많이 쓰이는 저장장치는 eMMC로, 하나의 칩에 메모리 소자와 컨트롤러가 통합 패키지로 제공되는 방식이다. 컨트롤러 내부에 SRAM 소자가 집적돼 소자의 에러가 시스템 페일러를 발생시키기도 한다. 이때 발생하는 많은 고장 중 SRAM의 비트플립으로 인한 고장이 보고되고 있다. 이 문제를 해결하기 위해 시스템 레벨에서 SRAM으로 데이터를 이동시킬 때 ECC 알고리즘을 채택하는 경우가 증가하고 있으며, 이를 통해 대부분의 알파 입자로 인한 불량률을 대폭 감소시킬 수 있다. 소자의 제조 과정에서 소프트 에러율 민감도는 반도체 공정의 미세화가 진행될수록 증가해 초고순도의 재료, 공정의 개선, 반도체 소자의 둔감성(Hardening) 증가 기술을 적극 채용함으로써, 향후 강화되는 안전 기준을 만족하는 제품의 신뢰성 확보가 중요하다.

글: 이종원|웨스턴 디지털 Product Quality Engineering

자료제공: 웨스턴 디지털

그래도 삭제하시겠습니까?