[테크월드=선연수 기자]

위상 잡음 요인 ②

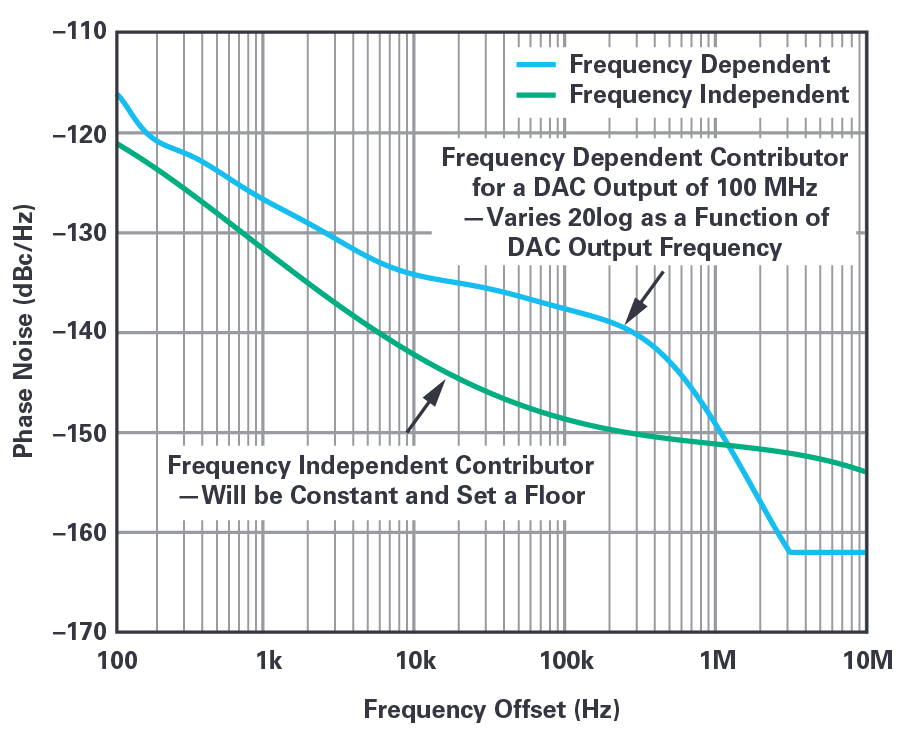

다음으로 트랜시버 IC 위상 잡음을 살펴보자. 송신 경로 상의 모든 회로 소자들로부터 잔류 잡음이 더해지는데, 이런 IC 잡음 요인 중 하나는 DAC 출력에서 첨가되는 잡음이다. 이는 DAC 출력 주파수에 따라서 달라진다. 잡음은 다시 주파수 종속적 잡음과 주파수 독립적 잡음으로 나뉜다. 주파수 종속적 잡음은 DAC 출력 주파수에 따라서 20logN으로 변하고, 주파수 독립적 잡음은 고정적이며 트랜시버 IC의 위상 잡음 플로어를 결정하게 된다.

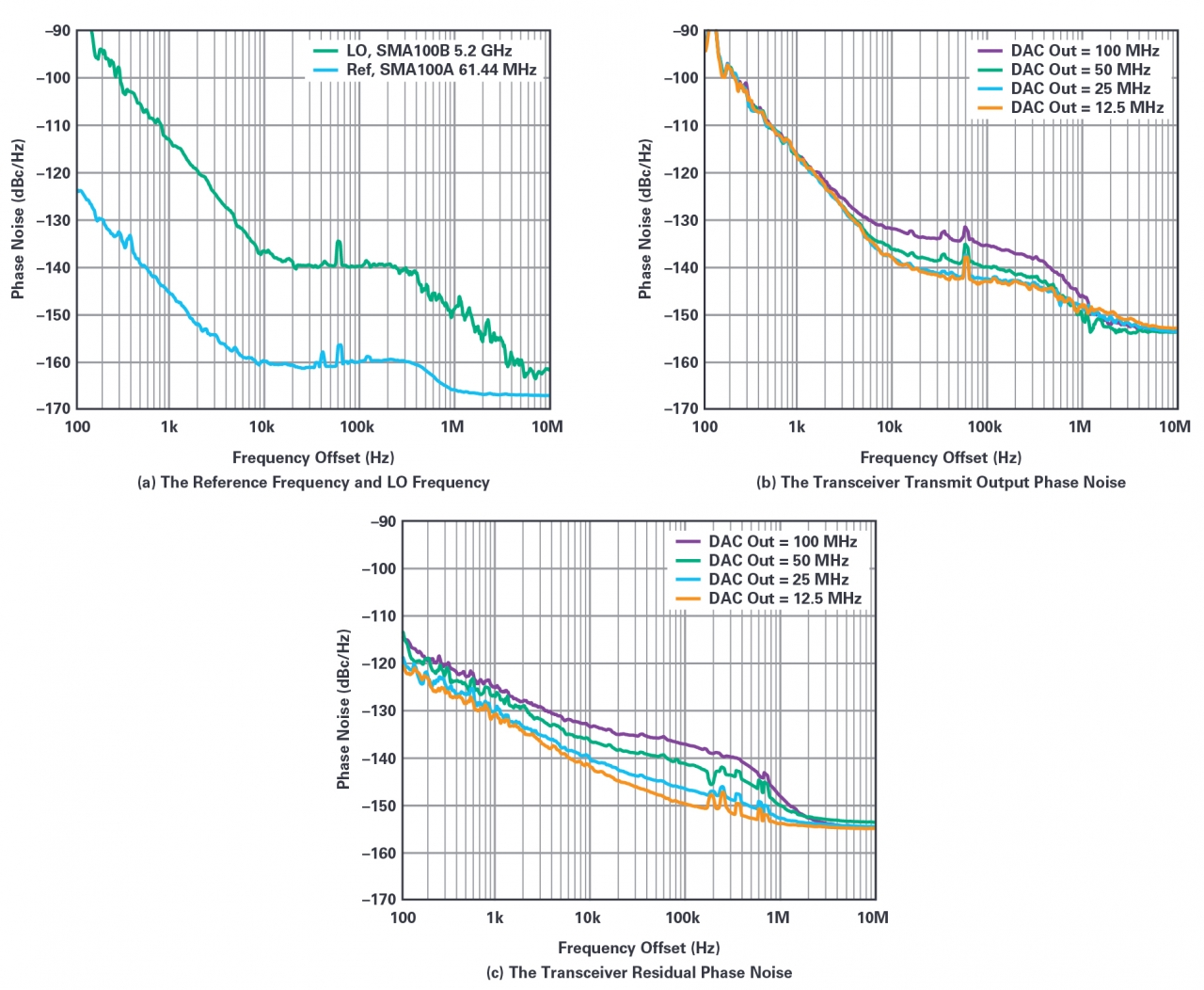

주파수 종속적 잡음과 주파수 독립적 잡음의 함수로 IC 잔류 잡음을 추출하기 위해, [그림 4]와 같이 일련의 위상 잡음 측정을 실시했다.

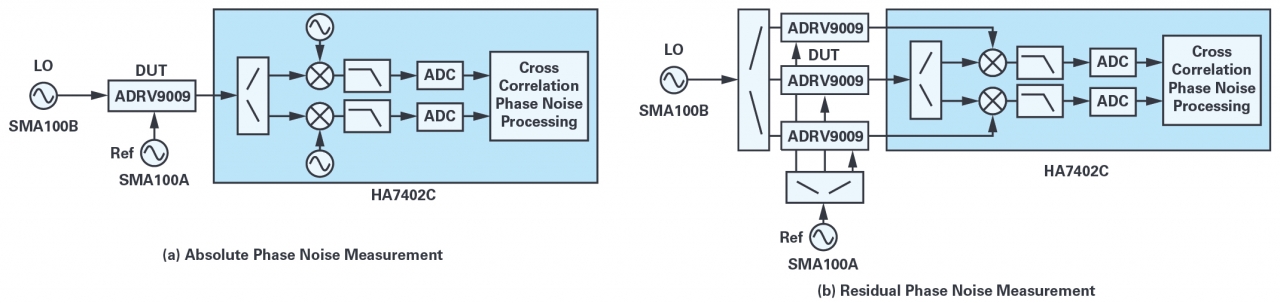

[그림 5]는 위상 잡음 측정에 사용된 테스트 셋업을 나타낸다. 트랜시버 LO와 레퍼런스 주파수 입력으로 각각 로데슈바르즈의 SMA100B와 100A를 사용했으며, 위상 잡음 테스트 세트로는 홀츠워스의 HA7402C를 사용했다. 절대 위상 잡음 측정을 위해 테스트 세트에 트랜시버의 송신 출력을 주입한다. 잔류 위상 잡음 측정을 위해서는 3개의 트랜시버가 필요하다. 추가적인 트랜시버를 테스트 세트 믹서의 LO 포트로 사용하면, 레퍼런스 주파수와 LO 주파수로 인한 잡음이 제거된 측정치를 얻을 수 있다.

[그림 6]은 [그림 4]의 측정 데이터로부터 트랜시버 IC로 인한 주파수 종속·독립적 위상 잡음을 추출한 뒤 계산한 값이다. 측정 데이터로 대입하고 1MHz 이상의 오프셋 주파수로 위상 잡음 플로어에 대해 임계 설정을 적용해 계산했다.

절대 위상 잡음 측정값 대 예측값

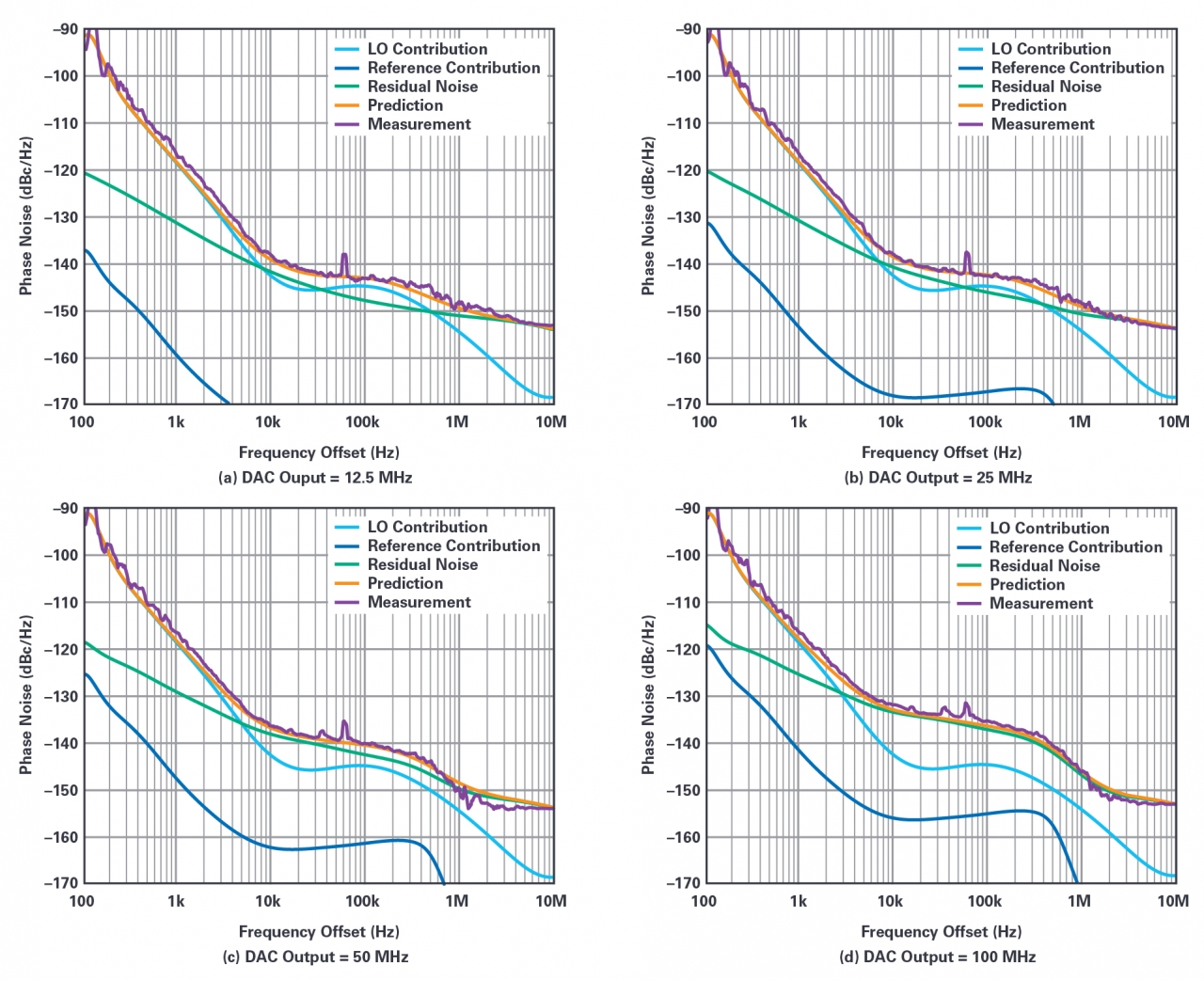

앞서 설명한 다양한 위상 잡음 요인들을 분석함으로써 DAC 출력 주파수와 LO, 레퍼런스에 사용된 오실레이터에 기반한 예측을 할 수 있다. [그림 7]은 측정 결과와 예측 결과를 비교한 그래프이며, 잡음 교인들은 다음의 계산법을 따랐다.

▲LO 위상 잡음: [그림 4]에서 측정된 LO 위상 잡음을 사용했으며, 트랜시버 IC 내의 주파수 분주기를 반영하기 위해 6dB 감소시켰다.

▲레퍼런스 위상 잡음: [그림 4]에서 측정된 레퍼런스 잡음을 시작점으로 사용했다. 트랜시버의 클럭 PLL은 루프 대역폭이 수백 kHz에 이르기 때문에 레퍼런스 잡음에 대해서 비슷한 대역폭의 2차 저역통과 필터를 적용했다. 그 다음, 잡음을 DAC 출력 주파수 대 레퍼런스 주파수 비의 20log로 변화시켰다.

▲IC 잡음: [그림 6]의 곡선 데이터를 사용했다.

트랜시버 중심 주파수가 2.6GHz이기 때문에 LO를 5.2GHz로 설정했다. DAC 출력 주파수는 12.5MHz부터 100MHz까지 다양하게 변화시켰다. 측정 결과가 예측값에 거의 일치하며, 그래프를 통해 오프셋 주파수들에 주로 영향을 미치는 요인들을 파악할 수 있다. 또한, 이 분석 기법을 다른 주파수로 확장해 적용할 수 있다. 5kHz 이하의 오프셋 주파수에는 1차 LO가 지배적이다. 1MHz 이상의 오프셋에는 IC 잔류 잡음이 지배적이다. 10~500kHz 사이의 중간 오프셋 주파수에서는 DAC 출력 주파수가 중요해진다. 높은 DAC 출력 주파수에서는 IC의 주파수 종속적 잡음이 지배적이다. DAC 출력 주파수가 낮아질수록 IC 잡음이 감소하고 LO 주파수가 다시 주요해진다.

외부 LO 사용 시 고려 사항

외부 LO를 사용할 때는 다음 2가지 사항을 유의해야 한다.

▲내부 주파수 분주기를 사용하면 스타트업하거나 외부 LO를 스위칭 할 때 위상 모호성이 있을 수 있다. RF 위상 동기 기능은 내부 LO에는 포함되나, 외부 LO는 아직 지원하지 않는다.

▲외부 LO를 호핑 할 때 QEC 알고리즘 안정화에 시간이 걸리며, 이 시간은 주파수 변경 직후 이미지에 영향을 줄 수 있다.

이런 문제들로 인해 동작 대역들 간에 트랜시버의 순시 대역폭 이상으로 동적 호핑을하는 다채널 시스템에 복잡성을 일으킬 수 있다. 이후 출시될 트랜시버들은 이런 한계점을 극복할 것으로 보이나, 현재는 ADRV9009에 외부 LO를 사용할 경우 이런 복잡성이 존재한다.

그러나 외부 LO의 향상된 위상을 활용할 수 있는 다양한 애플리케이션들이 존재한다. 이런 애플리케이션으로는 동적 호핑 요구가 덜 엄격한 단일 채널이나 채널 수가 적은 시스템, 또는 고정된 LO 주파수를 사용하는 다채널 시스템을 예로 들 수 있다.

상대적으로 협대역인 위상 배열 시스템은 특히 외부 LO의 위상 잡음 성능 활용에 적합하다. 이 애플리케이션에서는 범용 파형 생성기와 리시버 설계용으로 이 트랜시버를 사용해, 넓은 동작 주파수를 지원하도록 하고 실제 동작이나 최종적인 LO 구현 단계에서 특정 대역을 선택할 수 있다.

동작 대역이 트랜시버의 순시 대역폭 이내인 위상 배열 시스템은 외부 LO가 단일 주파수일 수 있으며, 이 경우 위상 배열로 트랜시버에 외부 LO를 사용하는 것이 실용적일 수 있다. 시스템 위상 잡음을 평가할 때 레퍼런스 주파수 잡음원이 LO 잡음원보다 훨씬 낮은 영향을 줄 경우, 레퍼런스 주파수 소스 오실레이터를 선택할 수 있다. 공통 LO를 배열된 트랜시버들로 분배할 때는, 시스템에 코히어런트하게 결합되는 트랜시버 수가 많아질수록 IC로 인한 잡음이 감소하고 외부 LO가 지배적이게 된다. 이를 통해 시스템 엔지니어링 잡음 분석을 간소화할 수 있다. 공통 LO가 대부분인 잡음은 엔지니어링 시 LO 설계의 가격대 성능비를 최적화하는 것에 초점을 맞출 수 있다.

결론

이 글에서는 외부 LO를 사용할 때 ADRV9009 트랜시버의 위상 잡음을 예측하는 기법을 설명했다. 이를 사용해 DAC 출력 주파수에 따라 레퍼런스 오실레이터, LO 소스, 트랜시버로 인한 잡음을 추적할 수 있다. 측정 결과와 예측 결과가 거의 일치하기 때문에, 다른 주파수 소스에 대해서도 이 기법을 적용해 트랜시버의 성능을 예측·분석할 수 있다. 이 기법은 상당히 일반적이기에 어느 파형 생성기 설계에라도 똑같이 적용할 수 있다.

외부 LO 사용 시 측정한 위상 잡음 성능을 보면, 위상 잡음이 낮은 LO 소스를 사용할 경우 상당한 성능 향상을 이룰 수 있다. 이 글의 목적은 시스템 설계 엔지니어들이 아키텍처를 검토하는 단계에서 다양한 선택을 할 수 있도록 돕기 위한 것이다. 낮은 위상 잡음을 요구하는 애플리케이션에서 이 트랜시버를 외부 LO 입력과 함께 사용할 경우, 앞서 설명한 기법을 이용해 다양한 조건으로 시스템 차원의 위상 잡음을 평가할 수 있다.

'외부 LO 사용 시 트랜시버 위상 잡음 예측 기법 ①'과 이어지는 기사입니다.

글: 피터 딜로스(Peter Delos) 테크니컬 디렉터

자료제공: 아나로그디바이스

- 이 글은 테크월드가 발행하는 월간 <EPNC 電子部品> 2020년 2월 호에 게재된 기사입니다.

그래도 삭제하시겠습니까?