[테크월드뉴스=이재민 기자] 오늘날에는 대역폭에 대한 수요가 폭발적으로 증가해 캐리어 주파수가 수십 ㎓(기가헤르츠)까지 이르게 됐다. 이처럼 높은 주파수에서는 스펙트럼 혼잡을 겪지 않고, 넓은 대역폭을 활용할 수 있다. 그러나 주파수가 높아지면 이런 디바이스와 주파수를 겨냥한 계측 솔루션은 극도로 복잡해질 수밖에 없다. 테스트 대상 디바이스(DUT)를 손상시키지 않기 위해서는 계측 솔루션에 차원이 다른 높은 성능이 요구되기 때문이다.

이 글에서는 위상 잡음이 낮은 신호를 생성하기 위한 다양한 방법에 대해 알아본다. 각 방법의 장단점을 살펴보고, 주파수 생성 방법들의 장점을 취하면서 복잡성은 제거하고 위상 잡음이 극히 낮은 신호를 생성할 수 있는 통합 수준이 매우 높은 변환 루프 디바이스를 소개한다.

PLL 회로 구조

PLL(위상 동기 루프) 회로는 많은 주파수 생성 장치에 흔히 사용된다. 이 회로는 생성하고자 하는 파형이나 신호를 레퍼런스 신호의 위상과 일치하게 만든다. [그림 1]은 PLL 회로의 블록 다이어그램이다. 전압 제어 오실레이터(VCO)의 출력을 N 카운터로 나누고, 위상/주파수 검출기(PFD)를 사용해 레퍼런스 신호와 비교한다. 이 간단한 회로는 많은 교재에서 중요하게 다뤄지고, 활발하게 연구되고 있는 주제다. 이제 출력에서 위상 잡음을 크게 낮출 수 있는 방법에 대해 알아보기로 한다.

![▲ [그림 1] PLL 회로](https://cdn.epnc.co.kr/news/photo/202109/214944_215052_649.png)

각 기능 블록의 불완전성이나 위상 잡음은 전체 PLL 회로의 위상 잡음에 기여한다. 각각의 블록과 관련한 위상 잡음은 모델링할 수 있고, 해당 PLL의 전반적인 위상 잡음은 시뮬레이션과 분석적 계산을 통해 정확하게 예측할 수 있다. 이들 각각의 블록을 살펴보고, 각 블록이 출력 위상 잡음에 어떻게 영향을 미치는지 살펴보자.

PFD 블록은 출력 주파수를 분주한 것을 레퍼런스 신호와 비교한다. 이 블록은 제어전압을 생성하는 차지 펌프 회로에 공급되는 오차 신호를 생성해 디바이스의 출력 위상이 레퍼런스 위상과 일치하도록 VCO를 조정한다. 내부에 PFD 회로를 통합하고 있는 대부분의 최신 주파수 생성기 제품은 데이터 시트상에 FOM(figure of merit) 정보를 제공한다. 이 FOM을 사용해 대역 내 위상 잡음을 다음과 같이 계산할 수 있다.

![▲ [그림 2] 위상 잡음을 계산하는 공식](https://cdn.epnc.co.kr/news/photo/202109/214944_215053_731.png)

이 공식에서 fPFD는 PFD 주파수고, N은 출력 주파수 분주기 값이다. 출력 주파수는 fPFD와 N 분주기 값을 곱한 것이다. 임의의 출력 주파수인 경우, fPFD가 특정 비율로 증가하면 N값은 같은 비율로 감소한다. 그 결과 전반적인 출력 위상 잡음을 낮춘다. N값이 감소하면 fPFD가 증가한 비율의 두 배만큼 위상 잡음을 낮출 것이다. PFD 주파수가 높을수록 근접 위상 잡음(close-in phase noise)은 낮아진다고 말할 수 있다. 이에 관해서는 뒤에서 더 살펴보기로 하겠다.

PFD 다음에는 루프 필터가 자리한다. 루프 필터는 PFD 디바이스로부터 전달되는 오차 신호를 매끄럽게 하고, 이 신호를 사용해 VCO를 제어한다. 이는 차지 펌프 전류, VCO 감도, PFD 주파수 등 시스템의 여러 파라미터를 사용해 설계된다. 루프 필터의 기능 중에서 크게 강조되지 않는 것 하나가 네거티브 피드백 제어 루프의 대역폭을 결정하는 것이다. 레퍼런스 신호는 루프 필터의 제어 대역폭 내에서 출력 신호의 위상 잡음에 영향을 미친다. 이 컷오프 주파수를 벗어나서는 VCO의 특성에 따라 전반적인 위상 잡음 성능이 결정된다. 뒤에서 살펴보겠지만, 이 점을 활용해 시스템의 전반적인 위상 잡음을 최적화할 수 있다.

VCO는 자신의 입력으로 주어지는 제어 전압에 따라 출력 주파수를 생성한다. VCO의 출력 주파수가 레퍼런스 신호와 위상이 일치할 때까지 제어 루프가 업데이트된다. VCO는 시스템의 전체적인 위상 잡음에 직접적인 영향을 미친다. 대체로 VCO의 Q값이 높을수록 위상 잡음은 낮아진다. 하지만 높은 Q값을 위해서는 조절 가능한 범위가 제한적인 부품을 사용해야 할 수 있다. 통상적으로 좁은 주파수 범위에서 동작하도록 설계된 VCO가 위상 잡음 성능이 가장 우수하다.

주파수 생성 방법들

신호를 생성하는 방법에는 여러 가지가 있다. 다양한 오실레이터 토폴로지를 사용하면 여러 Q값의 신호를 생성할 수 있다. 계측 애플리케이션은 위상 잡음이나 스퓨리어스 수준에서 되도록 높은 성능을 필요로 한다. 그러면 위상 잡음을 낮추면서 주파수를 생성하는 방법에 대해 알아보자.

고정 주파수 오실레이터를 사용한 주파수 생성

위상 잡음 성능이 우수한 신호 생성 디바이스로서 고정 주파수 오실레이터를 들 수 있다. 고정 주파수 오실레이터는 Q값이 매우 높고, 근접 위상 잡음 성능이 우수하다. 이 유형의 오실레이터는 사전에 설계된 주파수로 동작하며, 위상을 레퍼런스 소스로 동기화하도록 어느 정도 조절할 수 있다. 오븐 제어 크리스털 오실레이터(OCXO), 온도 보상 크리스털 오실레이터(TCXO), 전압 제어 SAW 오실레이터(VCSO) 등이 이런 유형의 디바이스들이다.

고정 주파수 오실레이터의 가장 큰 단점은 주파수 커버리지가 제한적이라는 것이다. 따라서 고정된 주파수나 그의 배수로 동작하는 애플리케이션에는 적합할지 모르나, 대부분의 계측 장비는 가변 주파수 커버리지를 필요로 한다.

![▲ [그림 3] 고정 주파수원을 사용해서 가변 주파수 생성](https://cdn.epnc.co.kr/news/photo/202109/214944_215054_1013.png)

이에 대한 해결책은 직접 디지털 합성(DDS) 디바이스나 디지털-아날로그 컨버터(DAC)를 사용하는 것이다. [그림 3]처럼 고정 주파수 신호를 사용해 DDS 디바이스의 샘플링 클럭을 구동할 수 있다. 주파수 체배기나 스텝 복구 다이오드(SRD)를 통해 필요에 따라 오실레이터 주파수를 체배시키고, 필터링한 후에 DDS로 전달한다. DDS는 1차 나이퀴스트 영역에서 샘플링 주파수의 최대 절반까지 임의 주파수를 생성할 수 있다. 일부 최신 DAC 디바이스는 2차 나이퀴스트 영역에서까지 별 문제없이 동작할 수 있다.

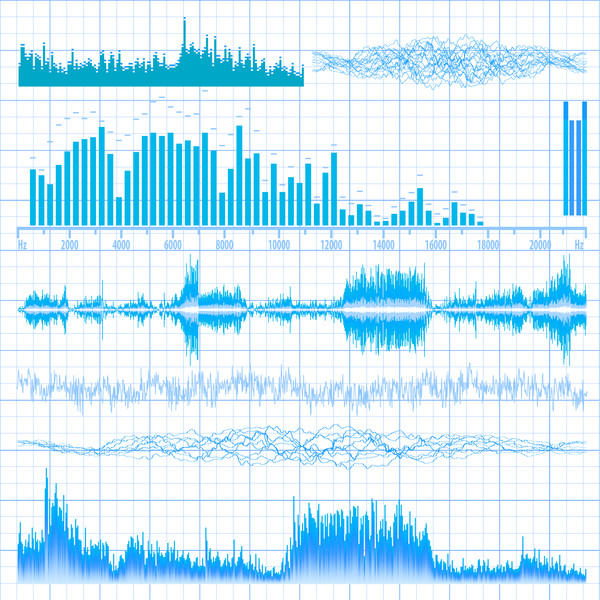

[그림 4]는 위상 잡음이 낮은 유전체 공진기 오실레이터(DRO)로 6㎓로 구동할 때 ‘AD9164’의 출력 스펙트럼과 위상 잡음 플롯을 보여준다. 위상 잡음 플롯을 보면 출력 위상 잡음이 놀라울 정도로 낮다는 것을 알 수 있으며, 출력 스펙트럼은 스퓨리어스가 -70dBc 미만이다.

![▲ [그림 4] 고정 주파수 오실레이터를 샘플링 클럭으로 사용할 때 800㎒에서 ‘AD9164’의 출력 스펙트럼과 위상 잡음](https://cdn.epnc.co.kr/news/photo/202109/214944_215055_1053.png)

체배시킨 샘플링 클럭의 스펙트럼 순도가 출력에 직접적인 영향을 미친다. 신호를 체배시키면 많은 고조파 성분이 출력에 생성된다. 원하는 신호를 필터링함으로써 DDS의 출력에 매우 낮은 스퓨리어스 수준을 달성할 수 있다. 통상 샘플링 클럭에 존재하는 스퓨리어스가 출력에서 비슷한 수준으로 나타난다. 체배율이 높은 경우에는 필터를 극도로 가파르게 해야 하는데, 그러려면 필터가 상당한 면적을 차지하게 된다.

또한 체배율이 높아질수록 체배 신호의 위상 잡음도 증가한다. 예를 들어 신호의 주파수를 두 배로 높일 때마다 위상 잡음은 6㏈씩 증가한다. 시작할 때의 위상 잡음 프로파일과 체배율에 따라 잡음 플로어(원격위상 잡음)가 크게 증가할 수 있다. 그러면 전반적인 솔루션의 유용성을 떨어트릴 것이다. 이는 널리 알려진 딜레마로서, 단일 주파수의 근접 위상 잡음을 활용하려고 하면 높은 Q-팩터의 디바이스가 원격위상 잡음 플로어가 불리해진다는 것이다.

예를 들어 표면 탄성파(SAW) 디바이스는 약 1㎓의 캐리어 주파수에서 우수한 근접 위상 잡음 성능을 갖는다. 하지만 40㎓ 이상으로 동작하는 밀리미터파 장비는 높게는 40 정도의 체배율을 필요로 한다. 그러면 위상 잡음 플로어가 32㏈ 이상 증가할 수 있어 이 솔루션은 매력적인 솔루션이 되지 못할 것이다.

광대역 PLL 디바이스를 사용하는 주파수 생성

광대역 합성기를 사용하면 단일 주파수 디바이스와 관련한 문제들을 해결할 수 있다. 이런 디바이스로서 ‘ADF4372 마이크로파 합성기’는 여러 개의 중첩된 대역으로 분할된 다중의 VCO 코어를 사용한다. 이런 아키텍처는 각각의 코어와 대역이 높은 Q값을 갖게 함으로써 단일 코어를 사용하는 아키텍처에 비해 전반적인 성능을 크게 향상시킨다.

이런 디바이스의 가장 큰 장점은 크리스털 오실레이터나 SAW 기반 오실레이터에 비해 기본 주파수가 더 높다는 것이다. 많은 최신 VCO는 기본 주파수가 4㎓부터 20㎓ 혹은 그 이상이 되기도 한다. 따라서 밀리미터파 애플리케이션에서 원격위상 잡음을 훨씬 좋게 한다. 일례로 10㎓ 기본 주파수로 동작하는 디바이스는 주파수를 40㎓까지 확장하려면 4의 체배율이 필요하다. 이는 위상 잡음 플로어를 12㏈ 증가시키는 것에 해당된다. 이와 달리 크리스털 오실레이터를 사용하면 32㏈ 증가한다.

이런 다중코어 및 다중대역 디바이스의 한 가지 과제는, 목표 주파수를 합성하기 위해 최적의 대역을 탐색하는 것이다. 이것은 룩업 테이블을 생성하고 적합한 대역을 찾게 하는 식으로 해결할 수 있다. ‘ADF4372’나 ‘ADF5610’처럼 오토캘리브레이션 기능을 갖춘 제품은 이 프로세스가 훨씬 수월하며, 온도와 프로세스 변화에 대해 강건한 특성을 갖고 있어 전반적인 작동을 크게 간소화할 수 있다. 주파수 변경을 단지 레지스터로 프로그래밍하기만 하면 가장 적합한 대역이 자동으로 결정되기 때문이다.

이 방법의 또 다른 과제는 단일 주파수 디바이스와 비교해 근접 위상 잡음이 훨씬 높다는 것이다. 전반적인 위상 잡음 플로어는 낮더라도 근접 위상 잡음이 높으면 적분 잡음이 높아질 수 있다. 그러면 낮은 적분 위상 잡음을 필요로 하는 애플리케이션에 사용하기엔 제한이 있을 수 있다.

변환 루프 기법

변환 루프 기법은 위에서 열거한 주파수 생성 방법들의 단점은 버리고 장점들만 취한 것이다. 변환 루프에 대해 알아보기에 앞서 지금까지 살펴본 방법들을 정리해 보자.

OCXO, SAW, 크리스털 오실레이터 같은 단일 주파수 디바이스는 Q값이 높고 근접 위상 잡음이 우수하다. 단일 주파수 디바이스들은 낮은 기본 주파수로 동작하므로 밀리미터파 주파수로 체배시켰을 때 원격위상 잡음이 나빠질 수 있다. 이런 디바이스의 근접 성능은 취하면서 원격위상 잡음의 불리함은 없앤다면 이상적인 솔루션이 될 수 있다.

DDS나 DAC 디바이스를 사용하면 고정 주파수 디바이스로 가변적 주파수를 생성할 수 있다. 이런 디바이스들 역시 밀리미터파 주파수를 위해 높은 체배율이 필요하며, 부고조파와 기타 원치 않는 스퓨리어스를 제거하기 위해서는 필터링이 필요하다. 이런 문제들을 해결함으로써 이상적인 솔루션을 달성할 수 있다.

광대역 합성기는 기본 주파수가 매우 높고, 원격위상 잡음 성능이 우수하다. 그러나 이 디바이스는 Q값이 높지 않으며, 단일 주파수 디바이스에 비해 근접 위상 잡음이 상대적으로 나쁘다. 그러므로 근접 위상 잡음을 저하시키지 않으면서 원격위상 잡음 성능을 활용할 필요가 있다.

이런 과제들을 해결하기 위해 개발된 것이 [그림 5]와 같은 변환 루프 디바이스다. 이 회로에서는 출력 주파수를 높은 분주기 값으로 나누는 것이 아니라, 주파수 믹서를 사용해 출력 신호를 레퍼런스 신호의 주파수와 일치하는 중간 주파수(IF)로 변환한다. 이렇게 함으로써 분주기 값을 실질적으로는 1로 낮춰 통상적인 PLL 회로에서처럼 높은 분주기 값으로 인해 비롯되는 잡음을 제거할 수 있다.

한편 이렇게 하면 LO의 위상 잡음 프로파일이 제어 루프로 더해진다. 그러므로 근접 성능이 우수한 단일 주파수 디바이스에 DDS를 사용해 이 LO 신호를 생성할 수 있다.

![▲ [그림 5] 변환 루프 아키텍처](https://cdn.epnc.co.kr/news/photo/202109/214944_215056_1253.png)

변환 루프를 위해서는 루프 필터 대역폭이 설계상의 중요한 파라미터다. 앞서 살펴본 것처럼 루프 필터가 전체 제어 루프의 대역폭을 결정한다. 다시 말해 레퍼런스와 LO 신호가 출력 위상 잡음에 얼마나 멀리까지 영향을 미칠지 결정한다. 변환 루프는 근접 위상 잡음이 극히 낮으므로 높은 루프 필터 대역폭을 선택할 수 있다.

[그림 6]은 변환 루프 디바이스와 LO 입력의 위상 잡음 프로파일을 보여준다. LO를 보면 근접 위상 잡음은 극히 낮고, 원격잡음 플로어는 높다는 것을 알 수 있다. RF 출력은 루프 필터 대역폭에 이르기까지는 LO 위상 잡음과 거의 비슷하나, 이 주파수 오프셋을 지나서는 원격위상 잡음이 VCO에 따라서 결정되며 이 잡음이 극히 낮다는 것을 알 수 있다.

![▲ [그림 6] 변환 루프 디바이스의 위상 잡음 프로파일](https://cdn.epnc.co.kr/news/photo/202109/214944_215057_1316.png)

변환 루프는 DDS 디바이스를 사용한 단일 주파수 디바이스의 바람직한 근접 성능을 활용하면서 높은 루프 대역폭을 선택한다. 이로써 광대역 VCO의 원격위상 잡음 이점을 활용할 수 있어 위상 잡음 구간을 어떻게 최적화할지에 대한 잘 알려진 딜레마를 극복할 수 있을 뿐만 아니라 극히 낮은 출력 위상 잡음을 달성할 수 있다.

변환 루프의 우수한 위상 잡음 성능은 많은 밀리미터파 계측 애플리케이션에서 매우 유용하다. 계측 솔루션은 위상 잡음 성능과 함께 스퓨리어스 신호도 극히 낮은 수준으로 억제해야 한다. 이것이 변환 루프에서 매우 까다로운 과제다. 서로 다른 주파수에서 다수의 강력한 신호가 존재하기 때문이다. 강력한 신호가 많은 경우에는 LO와 IF 신호가 출력으로 유입되지 않도록 하는 것이 매우 어려울 수 있다. 뿐만 아니라 출력에 IF, LO, RF 신호의 혼변조 성분들이 생성될 수 있다. 이런 스퓨리어스 신호들이 계측 솔루션 전반적으로 스퓨리어스 특성을 나쁘게 할 수 있다.

아나로그디바이스(ADI)의 통합 수준이 매우 높은 변환 루프 디바이스인 ‘ADF4401A’는 앞서 살펴본 많은 과제를 해결한다. 무엇보다 디스크리트 구현에 존재할 수 있는 모든 유입 경로를 제거한다. 이것은 디바이스 자체에 차폐 기능을 포함시킴으로써 유입 메커니즘을 최소화하도록 설계됐기 때문이다. 뿐만 아니라 스퓨리어스 제거가 -90㏈c에 이르는데, 이는 이트륨 철 가닛(YIG) 구 기반(sphere-based) 오실레이터 솔루션에 맞먹는다.

![▲ [그림 7] (a) 6.5㎓에서 변환 루프 출력 스펙트럼과 (b) 3㎓에서 LO 입력 스펙트럼. ADF4401A의 내부 LO 주파수 2체배기를 사용하면 유효 LO 주파수는 6㎓가 된다. IF 주파수는 500㎒다](https://cdn.epnc.co.kr/news/photo/202109/214944_215059_1514.png)

또한 이 디바이스는 입력이 덜 이상적일 때라도 출력에서 낮은 스퓨리어스 수준을 달성한다. [그림 7]의 (a)는 [그림 7]의 (b)와 같이 LO 입력에 약 -40㏈c에 이르는 여러 스퓨리어스 성분이 포함될 때, ADF4401A의 출력 스펙트럼을 보여준다. 통상적으로 이런 수준의 LO 신호는 상당한 양의 필터링을 필요로 하므로 계측 애플리케이션에 적합하지 않다. 그런데 ADF4401A는 추가적인 필터링 없이 이런 LO 입력을 수용할 수 있으며, [그림 7]의 (a)와 같은 출력 스펙트럼을 발생한다.

또한 이 디바이스는 오토캘리브레이션 엔진을 포함해 목표 주파수에 가장 적합한 VCO 대역을 자동으로 결정할 수 있다. 이 디바이스는 캘리브레이션 모드로 설정하면 실제 온도와 프로세스 조건에 가장 적합한 대역을 탐색한다. 그러므로 주파수 튜닝 프로세스를 간소화한다.

맺음말

계측 솔루션은 밀리미터파 애플리케이션의 요구를 충족하기 위해 위상 잡음이 극히 낮은 캐리어 신호에 극히 낮은 스퓨리어스를 필요로 한다. 이런 신호를 합성하기 위해서는 여러 방법을 사용할 수 있는데, 각각의 방법이 장점과 단점을 절충해야 하므로 솔루션들이 갈수록 복잡해지고 있다.

ADI의 변환 루프 디바이스인 ADF4401A는 여러 주파수 생성 방법들의 단점은 버리고 장점만을 취하고 있다. 그럼으로써 복잡한 필터링이 필요 없고, 극히 낮은 위상 잡음에 매우 우수한 스퓨리어스 성능을 달성한다.

글 : 에르칸 아카르(Erkan Acar) RF 시스템 설계자

자료제공 : 아나로그디바이스(www.analog.com)

그래도 삭제하시겠습니까?