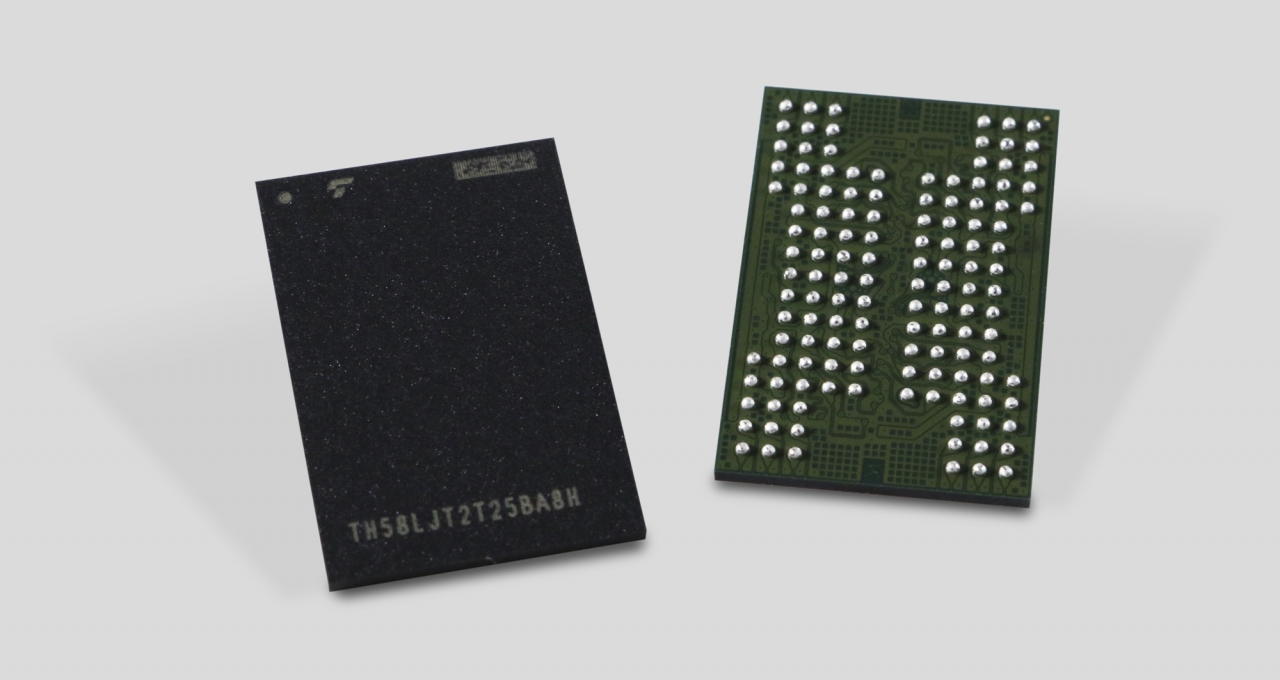

설어레이 밀도 20%, 인터페이스 속도 50% 향상

[테크월드=김경한 기자] 키옥시아(Kioxia Corporation)가 112층 3차원 수직 적층 공정 기술로 제작한 플래시 메모리인 5세대 빅스 플래시(BiCS FLASH)를 개발했다.

키옥시아의 112층 적층 공정 기술은 첨단 회로, 제조 공정 기술과 결합해 셀어레이 밀도를 96층 적층 공정에 비해 약 20% 향상했다. 새로운 기술은 비트당 비용을 절감하고 실리콘 웨어퍼당 생성되는 메모리 용량을 늘려준다. 또한 인터페이스 속도를 50% 향상시키고 우월한 프로그래밍 성능과 더 짧아진 읽기 대기시간을 제공한다.

5세대 빅스 플래시(BiCS FLASH)는 제조 파트너인 웨스턴 디지털(Western Digital Corporation)과 공동 개발했다. 제품은 키옥시아의 욧카이치 공장(Yokkaichi Plant)과 새롭게 설립된 기타카미 공장(Kitakami Plant)에서 생산된다.

키옥시아는 2020년 1분기에 특정 애플리케이션을 위해 3중셀(triple-level cell, TLC) 기술 기반 512기가비트(64기가바이트) 용량의 새로운 제품 샘플을 출하할 계획이다. 이 신제품은 기존의 모바일 기기, 소비자와 엔터프라이즈 SSD, 새로운 5G 네트워크, 인공지능, 자동차 기술에 의해 구현되는 신흥 애플리케이션을 포함해 다양한 적용 분야에서 지속적인 수요 증가에 대응할 수 있을 것으로 보인다.

키옥시아는 앞으로 새로운 5세대 공정기술을 1테라비트(128기가바이트) TLC와 1.33테라비트 4중셀(quadruple-level cell, QLC) 소자 등 더 큰 용량의 제품에도 적용할 계획이다.

그래도 삭제하시겠습니까?