[테크월드=이건한 기자] 매스웍스가 매트랩(MATLAB)과 시뮬링크(Simulink) 최신 버전 '2019b(R2019b)'에 포함된 HDL 베리파이어(HDL Verifier)의 FPGA, ASIC 설계를 위한 범용 검증 방법론(UVM) 지원 기능을 발표했다.

UVM(Universal Verification Methodology)은 2009년 전자설계자동화 분야의 표준화 기구인 엑셀레라(Accellera)에서 수립한 통합 회로 설계 검증의 표준 방법론이다. UVM 클래스 라이브러리는 시스템 베리로그(SystemVerilog) 언어에 적용 가능한 자동화를 지원한다.

최근 윌슨 리서치 그룹(Wilson Research Group)에서 실시한 연구조사 결과에 따르면, 약 48%의 FPGA 설계 프로젝트, 그리고 약 71%의 ASIC 설계 프로젝트에서 엔지니어 및 설계자들은 설계 검증을 위해 UVM을 사용하고 있는 것으로 나타났다.

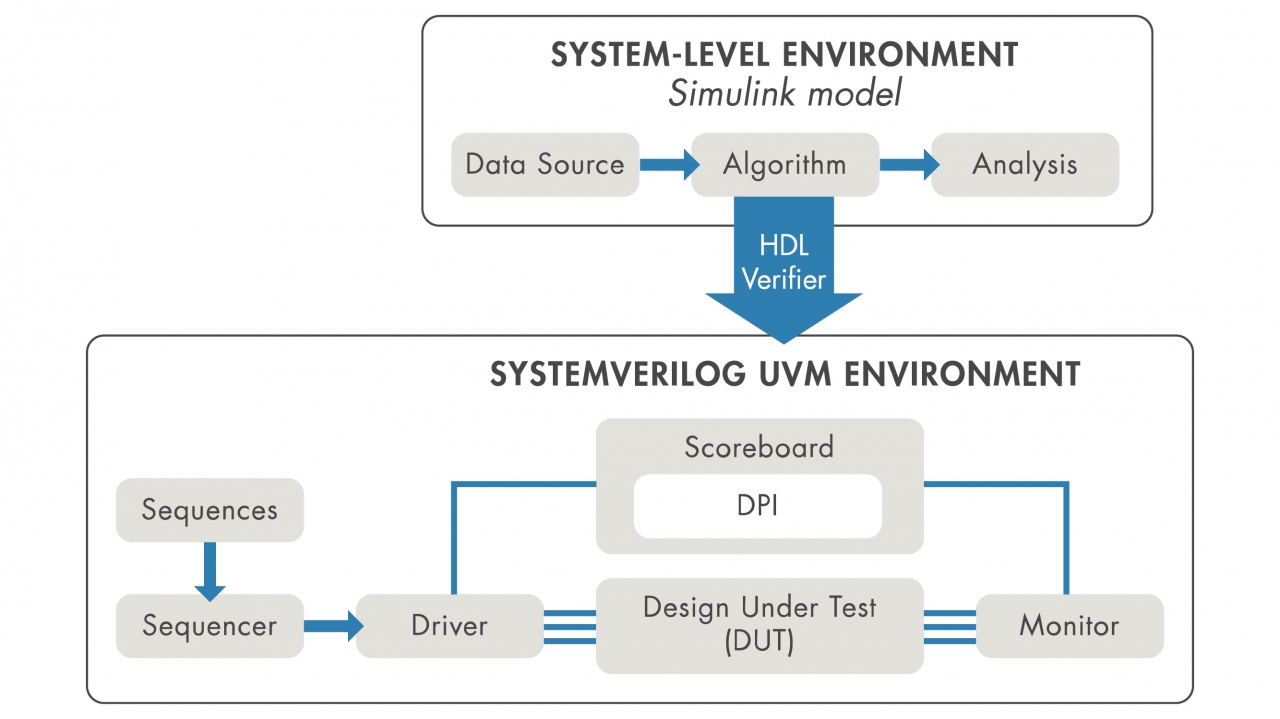

알고리즘 개발자와 시스템 설계자들은 주로 매트랩과 시뮬링크를 통해 새로운 알고리즘을 개발한 후, 설계검증(DV) 엔지니어가 이들 모델을 참조해 RTL 테스트 벤치를 직접 코딩한다. 이때 HDL 베리파이어를 사용하면 시뮬링크에서 개발된 시스템 레벨 모델로부터 시퀀스, 스코어보드 등의 UVM 컴포넌트를 자동 생성할 수 있기 때문에 수동으로 테스트 벤치를 작성하는 데 드는 많은 시간을 절약할 수 있다.

또한 이런 접근 방식은 검증 엔지니어가 무선 통신, 임베디드 비전과 제어 같은 분야에서 반도체 설계를 위한 테스트 벤치 개발 시간을 감소시키도록 돕는다.

매스웍스의 수석 HDL 제품 마케팅 매니저 에릭 시건(Eric Cigan)는 "이번에 발표한 HDL 베리파이어는 기존의 매트랩·시뮬링크 모델로부터 UVM과 시스템 베리로그 DPI 컴포넌트를 생성하는 새로운 기능을 통해 DV 엔지니어의 생산성을 높이는 동시에, 시스템 설계자, 하드웨어 엔지니어, DV 엔지니어 간의 협업을 개선할 수 있을 것으로 기대된다"고 말했다.

그래도 삭제하시겠습니까?