[테크월드=이나리 기자] 이 글에서 설명하는 마이크로컨트롤러는 32kB PCM(Phase Change Memory)과 8kB RAM을 포함하고, ARM 코어텍스(Cortex)-M4F 프로세서를 기반으로 모터 제어 기능을 통합하며, 전용 전원 스테이지와 아날로그 프론트엔드까지 포함한다.

이 마이크로컨트롤러는 DC/DC 컨버터에서부터 모터 구동에 이르는 다양한 스마트 전력 변환 애플리케이션에 사용하기에 적합하다. 또한 12V 과구동 내부 부트스트랩을 사용한 4개 2.5A 하프 브리지와 8개 0.3A 게이트 드라이버를 프로세서나 주변장치를 통해 최대 200kHz로 스위칭 할 수 있다. 또 3상 BLDC 모터의 자율적인 사인파와 6-스탭(Steps)을 구동할 수 있다. 더불어 BCD 0.11m 기술을 사용해 12.7mm2의 모노리딕 솔루션으로 구현됐으며, 단일 전원과 외부 IC용으로 3.3V, 5V를 제공할 수 있다.

I. 머리말

지난 수십 년간 전자 애플리케이션의 집적도는 놀랄 만큼 높아졌고, 이런 경향은 전원 시스템도 마찬가지다. 또 제어 로직, 신호 프로세싱, 전원 스테이지를 포함하는 포괄적인 전원 시스템을 단일의 시스템온칩(SoC)으로 통합할 수 있게 됐다. 최근에는 스마트 프로그래머블 플랫폼 시장이 성장하면서 이런 경향은 더욱 가속화되고 있으며, 특히 사물인터넷(IoT)과 산업용 IoT(IIoT) 분야의 전력 변환 애플리케이션이 많은 혜택을 누리게 됐다.

지능형 전력 반도체(IPE)에 매우 필요한 대표적 애플리케이션이 전원 애플리케이션 컨트롤러(PAC)와 브러시리스 DC(BLDC) 모터 드라이버이며, 이 시스템들은 비교적 대용량의 메모리를 필요로 한다. 플래시 기술을 2x nm 이하로 안정적으로 축소하고 액세스 시간을 단축하는 과제에 직면하면서 PCM을 비롯한 다양한 대안 기술들을 탐색하게 됐다. 이 글에서는 바로 이런 요구를 충족시키는 모노리딕 솔루션을 소개하며, 이는 의료용 애플리케이션, 자동차, 조명, 항공기 시스템에 적합하다.

II. 기술 설명

A. 프로세스의 주요 특성

단일 칩으로 포괄적인 시스템을 구현하기 위해서는 VLSI와 비휘발성 메모리가 가능한 전력 기술을 선택해야 한다. 이 기술은 새로운 BCD9sE로서 ST마이크로일렉트로닉스(STMicroelectronics, 이하 ST)의 Bipolar, CMOS, DMOS 0.11μm 기술이며, 상 변화 현상(PCM)에 기반한 비휘발성 랜덤 액세스 메모리를 갖추고 있다. 기본적인 프로세스 구성일 때, 이 기술은 최대 40V의 전압 정격과 2개의 게이트 산화막(아날로그 소자들은 위한 12nm 게이트 산화막과 1.8V 디지털 CMOS를 위한 3.5nm 게이트 산화막)을 특징으로 한다.

이 기술은 심층적 N+ 매립 층과 딥 트렌치 절연(DTI)을 적용해 인덕티브 부하를 견고하고 안전하게 구동할 수 있다. 또 신호 라우팅을 위한 3개의 얇은 박막 대머신(Damascene) 구리 금속층, 전원 전달을 위한 1개의 두꺼운 후막 구리 금속 층을 포함한 4개 금속층으로 완전한 구리 솔루션을 구현하고 있다. 디지털 부분의 최대 게이트 밀도는 최상의 조건에서 약 120000게이트/ mm2다.

B. 임베디드 메모리

BCD 플랫폼 용으로 개발된 PCM 솔루션은 접점 정의 후에 BEOL(Back End Of Line)을 통합하는 모듈러 기법을 특징으로 한다. MOS 드레인 접점 위로 저장 소자를 집적하고 이중 MOS에 의해 동적 영역 패터닝을 선택한다.

정보를 저장하기 위해서 사용되는 칼코겐화물(Chalcogenide)은 매 비트 셀에 얇은 수직 히터 위에 놓이는 띠로(비트 라인 방향을 따라) 정의된다. PCM에 있어 가장 어려운 과제는 리셋 상태일 때 저항 값의 드리프트다.

그 이유는 다중 레벨 애플리케이션에서의 사용이 어려워지기 때문이다. 이런 드리프트 동작은 온도에 대단히 종속적이며, 셀 온도에 따라 드리프트 특성에 대한 검토가 필요하다. 하지만 최근 칼코겐화물 구조가 개선되고 리딩 회로로 차동 기법을 사용함으로써, 개발된 PCM이 CMOS, 전력 디바이스 동작과 완벽하게 호환 가능하고 자동차용으로서의 신뢰성을 달성할 수 있게 됐다.

III. 칩 특성

이 칩은 전원 스테이지, 32비트 ARM 코어텍스-M4F 마이크로컨트롤러, 새로운 PCM을 통합한 최초의 모노리딕 디바이스다.

이 칩은 3.7V~40V의 넓은 전압 범위로 동작하고, 내부적 선형 레귤레이터를 통해 다양한 전원 전압(1.8V 100mA, 3.3V 100mA, 5V 500mA, 외부 MOS 게이트 소스 전압을 위한 12V), 과전류, 단락 회로, 열 보호 등의 보호 기능 등을 제공한다. 모든 레귤레이터 출력을 외부 소자를 구동하는 데 사용할 수 있으며, 5V 레귤레이터는 높은 전류를 공급하기 위해 외부 전력 MOS용 게이트 드라이버로 자동적으로 동작할 수 있다.

A. 전원 스테이지

이 디바이스의 전원 스테이지는 4개 하프 브리지와 8개 게이트 드라이버로 이뤄졌다. 하프 브리지들은 이중 본딩 와이어를 사용해 최대 2.5A의 듀얼 NMOS 토폴로지(측면 당 150mΩ Ron)로 구현됐으며, 각 상측에 전용 차지 펌프를 사용해 최대 35V로 동작할 수 있다. 또한 단락 보호, 프로그래머블 출력 슬루율, 상측과 하측 정류 사이에 적응식·프로그래머블 데드타임, 열 셧다운, 접지 본딩 와이어 저항의 켈빈 측정을 통한 전류 검출 등을 특징으로 한다.

게이트 드라이버는 4개의 독립형 듀얼 NMOS 외부 하프 브리지를 지원할 수 있으며, 상측과 하측 정류 사이에 조정·프로그래머블 데드타임을 설정할 수 있고, 내부 다이오드와 외부 커패시터를 사용한 부트스트랩 토폴로지를 적용하며, 전용 12V 레귤레이터를 사용해 외부 MOS용으로 Vgs를 제공한다. 이 레귤레이터를 정지시키고 외부적으로 다른 전압 소스를 사용할 수도 있다.

B. 아날로그 프론트 엔드

아날로그 프론트 엔드(AFE)는 12비트 2Msps SAR ADC 컨버터, 10비트 DAC(R2R 토폴로지), 15비트 DAC(2개 저항 스트링 토폴로지) 컨버터, 레일-투-레일 프로그래머블 이득 증폭기, 2개 레일-투-레일 1.8V 범용 비교기, BEMF(Back Electro-Motive Force) 검출용인 2개 레일-투-레일 40V 비교기를 포함한다.

C. 디지털 블록과 메모리

이 디바이스에 내장된 디지털 부품의 주요 특징은 마이크로컨트롤러와 관련된다. 이는 32비트 40MHz로 실행되는 ARM 코어텍스-M4F 코어를 기반으로 하며 디지털 신호 프로세서(DSP), 부동소수점 유닛(FPU), 3개의 범용 16비트 타이머를 포함한다. 또한 외부 상호작용을 위해 18개 범용 I/O 포트(그 중 6개는 30mA의 높은 전류 가능)를 제공한다. 통신은 I2C와 SPI 프로토콜을 통해 가능하며, JTAG와 SWD(Serial Wire Debug) 프로토콜을 통해 온칩 디버그를 지원한다.

D. 메모리

이 디바이스의 비휘발성 메모리는 선형 모듈 어레이를 기반으로 한 PCM이다. 32kB는 사용자 데이터용이고, 1kB 메모리는 트리밍과 설정 데이터용이다. 차동 기법(각 비트에 대한 직접, 상보적 셀)을 사용해 데이터 리드아웃을 한다. 이 어레이에는 에러검출 비트 라인들이 제공되며, 에러검출 재구성은 파워온 시 처리돼 메모리 액세스 시간에 영향을 미치지 않는다. 또한 이 칩은 스태틱(Static) RAM으로 8kB 메모리를 내장했다.

E. NTG(Numerical Torque Generator) 주변장치

이 칩은 자율적 3상 모터 구동을 할 수 있도록 NTG(Numerical Torque Generator)라는 전용 주변장치를 통합하고 있다. 따라서 마이크로컨트롤러의 연산 부담을 덜고 전력 소모를 낮출 수 있으며, 이를 통해 남는 연산 자원을 다른 작업에 사용할 수 있다.

NTG 주변장치의 주된 용도는 3상 브러시리스 모터를 구동하는 것이다. 로터 위치 정보에 따라 루프를 폐쇄하고 BEMF 피드백 신호 제로 크로싱을 검출한다. 내부 비교기는 3개 위상 중의 하나와 저항 네트워크를 사용해 재구성된 가상 CT(Center Tap) 사이에 연결된다. 디지털 마스크를 적용해 부정한 검출을 방지하고, 검출 간격 동안 해당 위상은 하이 임피던스 상태에 머문다. 이런 NTG 동작은 48개 샘플의 LUT(Look-Up Table)를 기반으로 하며, 6스텝(각 스텝에서 2개 위상 동작, 1개 위상은 하이 임피던스 상태) 구동과 사인파 구동을 모두 할 수 있다.

후자의 경우, 공간 벡터 변조 이론에서 시작해 [그림 6]에서처럼 인가되는 위상 전압을 변조함으로써 스위칭 전력 소모를 33%까지 낮추고 동일 배터리 전압에서의 각 위상 당 가용 전압을 15% 증가시킨다. LUT 샘플은 진폭 변조를 통해 수동으로든 자동으로든 다른 입력에 따라 과전류 검출, 전류 극성 반전, 로터 속도 제어 등 각기 다른 토크를 발생시킨다. 스위칭 데드 타임 시 한 위상의 출력 전압을 검출해 직접적으로 전류 극성을 검출한다.

이 때 전류는 프리휠링 다이오드를 통해 흐른다. BEMF 제로 크로싱 신호로부터 로터 속도를 계산하고, SCL(Speed Control Loop) 루틴은 계수 프로그래밍이 가능한 PI 컨트롤러를 사용해 LUT 진폭을 변조한다. 토크 옵티마이저(Torque Optimizer) TO 루틴은 전류 제로 크로싱을 검출해서 LUT 샘플에 대해 최대 +30의 위상 편이를 적용할 수 있다. 이를 통해 실제 사인파 전류와 BEMF 신호 사이에 스테이터 권선의 L-R 조합에 의해 발생된 위상 편이를 보정할 수 있다. 초기의 로터 스타트업과 스핀업은 스테이터 권선 인덕턴스를 검출해 개방 루프 조건(LUT는 소프트웨어로 수동 스캔)에서 수행할 수 있다.

이 경우 실제 로터 위치를 검출하기 위해 3개 스테이터 권선 중에서 2개를 순차적으로 활성화시키고 전류 임계값에 도달하는 시간을 계산한다. 내부 비교기가 전류 한계 신호를 제공하고, 이 임계값은 2개 DAC 중의 하나를 사용해 프로그래밍할 수 있다. NTG는 4개 내부 하프 브리지 중 3개 또는 8개 게이트 드라이버 중 6개로 연결할 수 있다. 특정 시점에 NTG로 연결되지 않은 모든 전원 스테이지는 2개의 범용 16비트 타이머에 의해 구동할 수 있다(1개는 하프 브리지용, 다른 1개는 게이트 드라이버용). 스위칭 주파수는 최대 200kHz로 프로그래밍할 수 있다.

F. 레이아웃

X-Spin의 복잡성에도 불구하고 정확한 설계와 레이아웃을 통해 경쟁력 있는 12.7mm2 크기의 단일 다이를 달성하게 됐다. 또한 전용 보호 회로(과열, 신속한 단락 검출, ESD 등)들을 포함해 높은 신뢰성과 안전성, 중복성, 디지털 제어, 모노리딕 솔루션을 달성했다.

G. 칩 성능

칩 기능과 성능은 정적 측정을 통해 평가했다. 각 하프 브리지로 2.5A를 공급하고 내부 하프 브리지는 최대 35V, 레귤레이터는 40V로 시스템을 구동했으며, 이를 3상 BLDC 모터 구동과 벅-부스트 스위칭 DC/DC 컨버터 등 두 가지 애플리케이션에서 실행했다. 이 칩은 노출 패드를 적용한 TQFP 64 플라스틱 패키지로 돼 있으며, 전용 PCB에 이 칩을 솔더링했다. 또한 ARM 코어텍스-M 프로세서용으로 상용과 무료 펌웨어 개발 툴 체인과 호환 가능한 온보드 디버거를 포함한다.

첫 번째 셋업의 경우, 내부 게이트 드라이버를 3개 외부 하프 브리지(Ron이 4.5m인 STL90N3LLH6)로 연결하고, 6개 극쌍으로 돼 있으면서 1000rpm/V의 Kv로 동작하는 AS2814 모터를 구동한다. 이 모터는 11” x 7” R CCW 프로펠러를 포함한다. 이 모든 시스템을 3셀 LiPo 배터리(11.1V)를 사용해 구동한다. 스위칭 주파수는 40KHz로 설정했다. NTG 주변장치로 사인파 PWM 프로파일을 직접 제공하며, 이를 통해 BEMF 제로 크로싱 검출에 따라 자동으로 루프를 폐쇄한다.

이제 코어텍스-M4 프로세서를 사용해 SCL 루틴의 목표 속도를 설정한다. 우리는 최대 7000rpm까지 동작을 테스트했으며, 평균 전류는 17A이고 총 추력(Thrust)은 1kg이었다. 또한 TO 루틴을 테스트했으며, 이는 동일하게 발생하는 토크에서 각 3개 위상의 전류를 줄이기 위한 것이다. 이런 조건에서 6500rpm으로 배터리 수준에서의 전류를 13.3A(위상 보정하지 않은 경우)에서 13A(위상 보정한 경우)로 낮추고, 결과적으로 전류 소모를 2.3% 낮출 수 있었다.

두 번째 셋업의 경우, 4개 내부 하프 브리지를 벅, 부스트, 벅-부스트의 3가지 토폴로지로 병렬 연결했다. 3개 토폴로지 모두, 800H 인덕터, 100F 커패시터, 프로그래머블 전류 부하를 사용했으며, 스위칭 주파수는 200kHz로 설정했다. 벅-부스트의 경우에는 2개 칩을 사용해 풀 브리지 아키텍처를 구현했다. 온칩 ADC를 사용해 PWM 생성과 동기적으로 출력 전압을 샘플링하고, 디지털 PI 컨트롤러를 구현해 PWM 듀티 사이클을 적응시키기 위한 펌웨어를 작성했다.

[그림 8]은 3개 아키텍처로 효율 측정을 보여준다. 스텝다운 동작은 30V, 스텝업 동작은 10V의 입력 전압으로 12V의 레귤레이트 전압을 제공하는 경우다. 효율 결과(η > 90%)를 보면 대부분 애플리케이션의 요구를 충족시키고 있다는 점을 알 수 있다.

H. 최신 제품들과의 비교

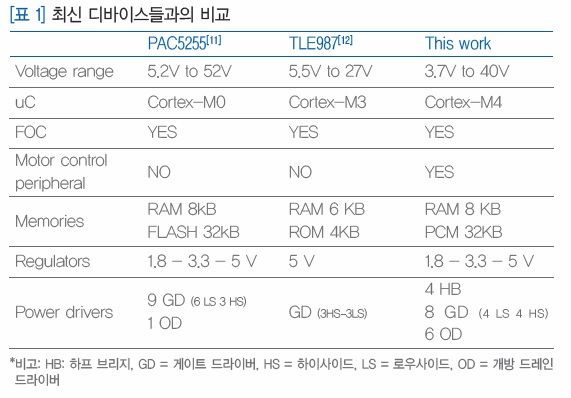

[표 1]은 이 디바이스와 다른 최신 디바이스들을 비교해 보여준다.

동작 전압 범위의 차이 말고도, 이 디바이스는 4개 하프 브리지와 8개 게이트 드라이버로 이뤄진 전원 스테이지를 포함하는 유일한 디바이스다. 이 칩이 현재 출시된 모터 제어 제품과 차별화되는 또 다른 특징은, 전용 NTG 주변장치를 포함한다는 점이다.

이를 통해 임베디드 마이크로컨트롤러의 처리 부담을 덜 수 있으며 더 많은 NTG 사례를 포함해 멀티코어 시스템으로 손쉽게 확장할 수 있다. 따라서 FOC(Field-Oriented Control) 알고리즘과 같이 모터를 실행하기 위한 특수한 펌웨어를 구현할 필요가 없어 훨씬 유리하다. 전력 소모를 줄이고 남는 연산 자원은 다른 작업에 할애할 수 있다.

맺음말

이 글에서는 지능적인 모터 구동과 전력 변환용으로 32kB PCM, 게이트 드라이버, 2.5A 전력 하프 브리지를 통합한 40V 모노리딕 마이크로컨트롤러에 대해 소개했다. 또한 이 디바이스는 비휘발성 메모리인 임베디드 PCM을 통합해 프로그래머블 모터 드라이버와 프로그래머블 DC/DC 컨버터(부스트, 벅, 벅-부스트)로 작동할 수 있다는 점을 알 수 있다.

글: ST마이크로일렉트로닉스 기술 R&D 엔지니어

주리 지오반논(Juri Giovannone), 알레산드로 니콜로시(Alessandro Nicolosi),

줄리오 리코티(Giulio Ricotti), 안드레아 베게티(Andrea Veggetti), 리타 자파(Rita Zappa)

그래도 삭제하시겠습니까?