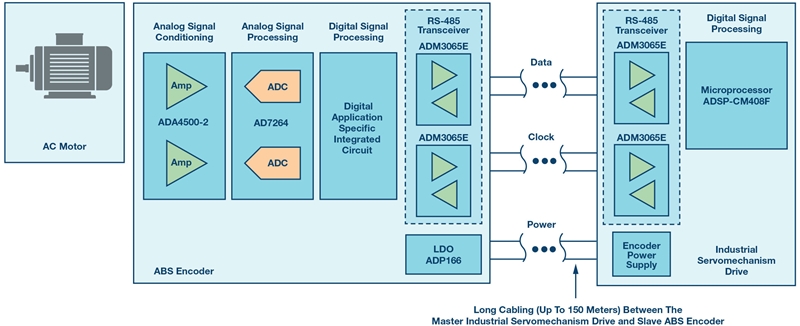

[테크월드=양대규 기자] 로터리 엔코더는 산업 자동화 시스템에 광범위하게 사용된다. 이런 유형의 엔코더는 회전축에 연결돼 제어 시스템에 피드백을 제공하는 전기 기계에 주로 이용된다. 엔코더의 주 목적은 각 위치와 속도 측정에 있지만, 시스템 진단과 파라미터 구성과 같은 추가적인 기능도 일반적이다. [그림 1]은 RS-485 트랜시버와 마이크로프로세서를 사용해 AC 모터의 폐쇄 루프 제어를 위해 절대 엔코더(ABS 엔코더) 슬레이브와 산업용 서보 드라이브 마스터를 연결하는 모터 제어 신호 체인을 보여준다.

서보 드라이브와 ABS 엔코더 간의 RS-485 통신 링크는 일반적으로 최대 16MHz의 높은 데이터 전송 속도와 낮은 전파 지연 타이밍 규격을 필요로 한다. RS-485 케이블 연결은 보통 최대 50m까지 연장되지만, 일부 경우 150m까지 확장할 수 있다. 모터 제어 엔코더 애플리케이션은 전기 잡음과 긴 케이블 길이가 RS-485 신호전송의 무결성에 영향을 미치기 때문에 데이터 통신에는 까다로운 환경이다. 이 글에서는 아날로그디바이스의 50Mbps(25MHz) ADM3065E RS-485 트랜시버와 ADSP-CM40x 혼합 신호 제어 프로세서를 사용해 구현하는 모터 제어 애플리케이션의 주요 이점을 살펴보기로 한다.

ADM3065E RS-485 트랜시버는 모터 제어 엔코더와 같은 열악한 환경에서 신뢰할 수 있는 동작을 제공하도록 설계됐으며 추가적인 잡음 내성(IEC)과 61000-4-2 정전기 방전(ESD) 내구성을 갖추고 있다.

잡음 내성

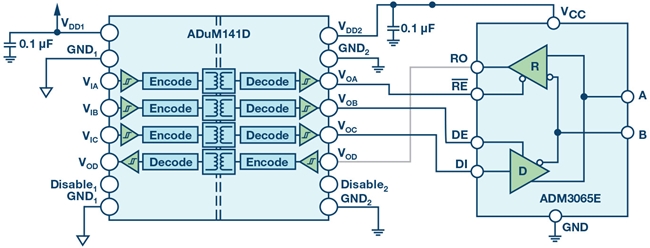

RS-485 신호 전송은 균형을 이루는 차동 방식으로 본질적으로 잡음에 강하다. RS-485 트위스트 페어 케이블에서 시스템 잡음은 각 와이어에 균등하게 결합된다. 하나의 신호는 다른 신호의 반대쪽으로 방사되므로 RS-485 버스로 결합된 전자기장은 서로 상쇄한다. 따라서 시스템의 전자기 간섭(EMI)이 감소된다. 이 밖에 향상된 ADM3065E 2.1V 드라이브 강도는 통신에서 신호대잡음비(SNR)를 증가시킨다. 또한, ADuM141D를 사용하면 ADM3065E에 쉽게 신호의 아이솔레이션을 향상 시킬 수 있다.

ADuM141D는 아날로그디바이스의 Coupler 기술을 기반으로 하는 쿼드 채널, 디지털 아이솔레이터이다. ADuM141D는 최대 150Mbps 데이터 전송 속도에서 동작할 수 있으므로 50Mbps ADM3065E RS-485 트랜시버와 함께 사용하기에 적합하다([그림 2] 참조). DPI(Direct power injection)는 전원장치나 입력 핀에 주입되는 잡음을 제거하는 디바이스의 성능을 측정한다. ADuM141D에 사용된 절연 기술은 DPI IEC 62132-4 표준에 따라 테스트했다. ADuM141D 잡음 내성 성능은 유사한 제품의 성능보다 뛰어나다. ADuM141D는 전체 주파수에서 탁월한 성능을 유지하지만, 다른 절연 제품은 200MHz~700MHz 주파수 대역에서 비트 오류를 보여준다.

IEC 61000-4-2 ESD 성능

노출된 RS-485 커넥터와 엔코더와 모터 드라이브를 연결하는 케이블에 존재하는 ESD는 공통적인 시스템 위험 요소다. 변속 전력 드라이브 시스템을 위한 EMC 내성 요구사항과 관련된 시스템 레벨 IEC 61800-3 표준은 최소 ±4kV 접촉 방전/±8kV 공기중 방전 IEC 61000-4-2 ESD 보호를 요구한다. ADM3065E는 ±12kV 접촉 방전/±12kV 공기중 방전 IEC 61000-4-2 ESD 보호로 이런 요구사항을 초과한다.

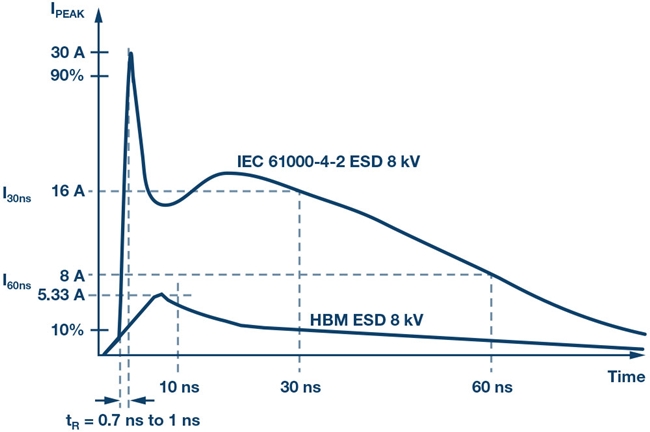

[그림 3]은 IEC 61000-4-2 표준의 8kV 접촉 방전 전류 파형을 HBM(human body model) ESD 8kV 파형과 비교한 것이다. 그림은 두 개의 표준이 서로 다른 파형과 피크 전류를 지정하고 있다는 것을 보여준다. IEC 61000-4-2 8kV 펄스와 관련된 피크 전류는 30A인 반면, HBM ESD에 대응하는 피크 전류는 5.33A으로 5배 이상 낮다. 또 다른 차이는 초기 전압 스파이크의 상승 시간이다. IEC 61000-4-2 ESD는 1ns로 HBM ESD 파형의 10ns에 비해 훨씬 빠른 상승 시간을 갖는다.

IEC ESD 파형과 관련된 전력량은 HBM ESD 파형의 전력량보다 훨씬 크다. HBM ESD 표준은 시험을 받는 장비(EUT)가 3개의 양극과 음극 방전 테스트를 받도록 규정하는 데 반해 IEC ESD 표준은 10개의 양극과 10개의 음극 방전 테스트를 요구한다. IEC 61000-4-2 ESD 등급의 ADM3065E는 서로 다른 수준의 HBM ESD 보호를 갖는 다른 RS-485 트랜시버보다 혹독한 환경에서 동작하는 데 더 적합하다.

EnDat 통신 프로토콜

엔코더에는 다양한 통신 프로토콜이 사용되는데, 예를 들면 EnDat, BiSS, HIPERFACE, Tamagawa 등이 있다. 엔코더 통신 프로토콜은 각기 다른 차이점에도 불구하고 구현과 관련해 유사점을 갖는다. 프로토콜의 인터페이스는 RS-422 또는 RS-485 전기 규격을 준수하는 직렬 양방향 파이프이다. 하드웨어 레이어에는 공통적인 특성이 있지만, 각 프로토콜의 실행에 필요한 소프트웨어는 고유하다. 통신 스택과 필요한 애플리케이션 코드는 둘 다 프로토콜에 특정하다. 이 글에서는 EnDat 2.2 인터페이스의 마스터 측의 하드웨어와 소프트웨어 구현을 살펴본다.

지연으로 인한 영향

지연은 다음 두 범주로 나눌 수 있다. 첫째, 케이블의 전달 지연과 둘째, 트랜시버의 전파 지연이 있다. 빛의 속도와 케이블의 유전체 상수가 케이블 지연을 결정하며, 일반적인 수치는 6ns/m에서 10ns/m 사이이다. 전체 지연이 클록 주기의 절반을 초과할 경우 마스터와 슬레이브 사이의 통신이 중단된다. 이 경우 설계자는 다음과 같은 옵션을 사용할 수 있다.

▲데이터 전송 속도를 낮춘다.

▲전파 지연을 낮춘다.

▲마스터 측에 지연 보상을 도입한다.

세 번째 방법은 케이블 지연과 트랜시버 지연을 둘 다 보상하므로 시스템이 긴 케이블에서 높은 클록 속도로 동작할 수 있게 보장하는 효과적인 방법이다. 이 방법의 단점은 지연 보상이 시스템 복잡성을 증가시킨다는 점이다. 지연 보상이 가능하지 않거나 짧은 케이블을 사용하는 시스템에서 짧은 전파 지연을 갖는 트랜시버를 사용하는 가치는 분명하다. 낮은 전파 지연은 시스템에 지연 보상을 도입하지 않고도 높은 클록 속도를 제공할 수 있게 한다.

마스터 구현

마스터 구현은 직렬 포트와 통신 스택으로 구성된다. 엔코더 프로토콜이 UART와 같은 표준 포트를 따르지 않기 때문에 대부분의 범용 마이크로컨트롤러에 있는 주변장치는 사용할 수 없다. 대신 FPGA의 프로그래밍 가능한 로직을 사용해 하드웨어에서 전용 통신 포트를 구현하고 지연 보상과 같은 첨단 기능을 지원할 수 있다. FPGA를 이용하는 방법은 유연하고 애플리케이션에 맞춰 조정할 수 있지만 단점도 있다. 프로세서에 비해 FPGA는 비용이 높고 전력 소모가 많으며 제품 출시에 비교적 긴 시간이 소요된다.

이 글에서 설명하는 EnDat 인터페이스 구현은 모터 제어 드라이브를 위한 프로세서인 아날로그디바이스의 ADSP-CM40x에서 수행됐다. ADSP-CM40x는 펄스 폭 변조기(PWM) 타이머, 아날로그-디지털 컨버터(ADC), 싱크 필터와 같은 모터 제어를 위한 주변장치 외에도 매우 유연한 직렬 포트(SPORT)를 탑재한다. 이 SPORT는 EnDat, BiSS와 같은 엔코더 프로토콜을 포함해 많은 프로토콜을 에뮬레이트 할 수 있다. ADSP-CM40x는 풍부한 주변장치 세트를 갖추고 있어 첨단 모터 제어를 수행할 수 있을 뿐 아니라 동일한 디바이스에서 엔코더에 인터페이싱할 수 있다. 즉, FPGA를 사용할 필요가 없다.

테스트 구성

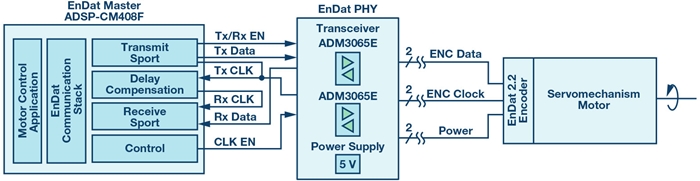

EnDat 2.2 테스트 구성은 [그림 4]에서 볼 수 있다. EnDat 슬레이브는 Kollmorgen의 표준 서보 모터(AKM22)이며 EnDat 엔코더(ENC1113)가 샤프트에 장착된다. 3쌍의 와이어(데이터, 클록, 전력선)가 엔코더를 트랜시버 보드에 연결한다. EnDat PHY에는 엔코더를 위한 2개의 트랜시버와 전원이 있다. 트랜시버 중 하나는 클록에 사용되고, 다른 트랜시버는 데이터 라인을 위해 사용된다. EnDat 마스터는 표준 주변장치와 소프트웨어를 사용하는 ADSP-CM40x로 구현된다. 송신 포트와 수신 포트는 둘 다 유연한 SPORT로 구현된다.

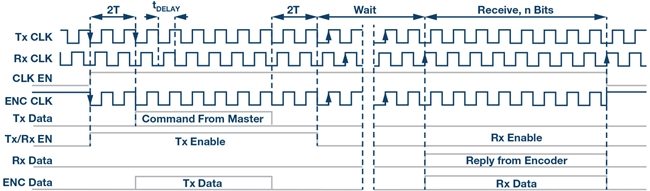

EnDat 프로토콜은 다양한 길이의 다수의 다른 프레임으로 구성된다. 그러나 [그림 5]에서 보듯이 이런 프레임은 모두 동일한 시퀀스를 기반으로 한다. 먼저 마스터가 슬레이브에 명령을 내리고, 다음으로 슬레이브가 명령을 처리하고 필요한 계산을 수행한다. 마지막으로 슬레이브가 결과를 마스터에 되돌려 보낸다.

송신 클록(Tx CLK)은 프로세서 ADSP-CM40x에 의해 발생된다. 시스템 지연으로 인해 엔코더의 데이터는 프로세서에 돌아가기 전에 송신 클록과 위상 차가 발생한다. 전달 지연 tDELAY를 보상하기 위해 프로세서는 송신 클록 대비 tDELAY만큼 지연시킨 수신 클록(Rx CLK)을 발생시킨다. 수신 클록을 슬레이브로부터 수신되는 데이터에 맞추어 위상을 정렬하는 것은 전달 지연을 보상하는 효과적인 방법이다.

프로세서에서 발생하는 클록 신호는 연속적이지만, EnDat 프로토콜은 통신 중 클록은 엔코더에만 인가해야 한다고 규정한다. 다른 모든 시간에 클록 라인은 하이로 유지해야 한다. 이를 처리하기 위해 프로세서는 ADM3065E의 데이터 인에이블 핀에 공급되는 클록 인에이블 신호 CLK EN을 발생시킨다. 정확히 두 번의 클록 주기(2T) 후에 마스터는 Tx DATA에 명령을 클로킹 아웃하기 시작한다.

명령은 6비트 길이이며, 다음에 2개의 0 비트가 이어진다. 트랜시버를 통해 데이터 방향을 제어하기 위해 프로세서는 송신하는 동안 Bit Tx/Rx EN을 하이로 설정한다.

슬레이브가 응답을 준비하는 동안 시스템은 대기 상태로 들어간다. 대기 상태에서 마스터는 클록을 계속 인가하지만 데이터 라인은 비활성화된다. 슬레이브가 응답할 준비가 되면 데이터 라인의 수신 데이터는 하이로 구동되고 응답은 그후 즉시 전송된다. n비트 응답을 수신한 후 마스터는 CLK EN 신호를 로우로 설정해 클록을 정지시킨다. 동시에 ENC CLK 신호는 하이가 된다. 데이터 흐름은 하프 듀플렉스이고 결합된 데이터 라인의 트래픽은 ENC 데이터로 나타난다.

시험 결과

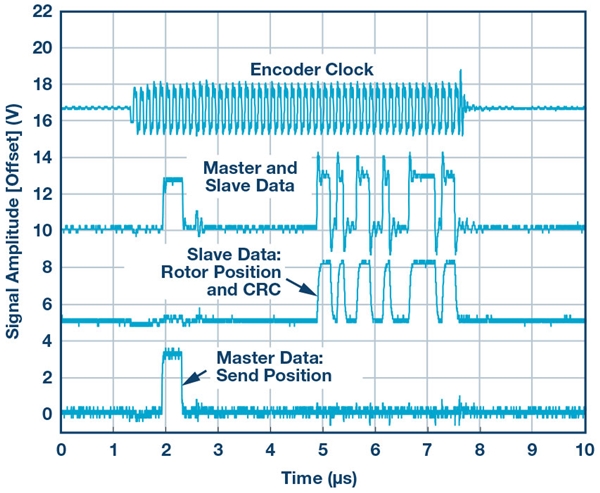

[그림 6]은 EnDat 시스템의 테스트 결과를 보여준다. 테스트에 사용된 클록 주파수는 8MHz이고 지연 보상은 수신 클록을 위상 이동해 달성된다. 맨 아래 신호는 EnDat 마스터 명령이다. 여기에 보이는 명령은 송신 위치, 즉 2개의 0에 이어 6개의 1이 오고 또 다른 2개의 0으로 종료된다. 전체 명령은 10비트 길이이다. 엔코더의 응답은 위에서 세 번째 신호이다. 결합된 데이터 라인은 위에서 두 번째 신호이다. 마지막으로 맨 위 신호는 엔코더에 인가되는 클록이다.

글: 젠스 소렌슨(Jens Sorenson), 리차드 앤슬로우(Richard Anslow)

자료제공: 아나로그디바이스

그래도 삭제하시겠습니까?