[테크월드뉴스=장민주 기자] 전력 시뮬레이션은 하드웨어 설계와 구축 전에 가정을 검증하고 구성 요소 설계와 선택, PCB 레이아웃, 테스트 절차에서 생기는 이슈 등을 밝혀내는 데 도움을 준다. 예를 들면 시뮬레이션을 통해 작동 전압과 전류, 스위칭 주파수, 전력 손실, 냉각 요건, 제어 알고리즘에 대한 다양한 상황을 테스트할 수 있다. 이런 검증과 함께 시뮬레이션 결과는 수동부품 선택처럼 개발 프로세스의 또 다른 중요 단계를 다룬다. 견고한 시뮬레이션은 개발 주기에서 디버깅과 하드웨어 반복을 줄여 제품 개발을 가속화한다.

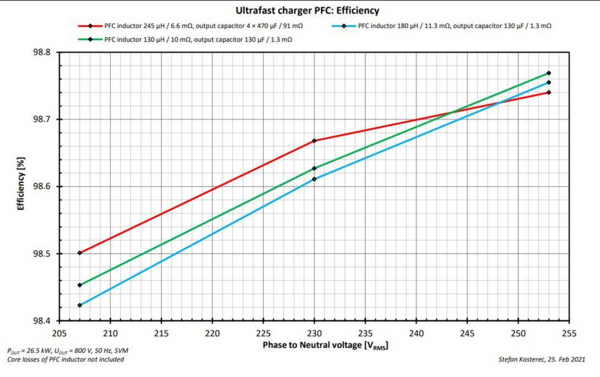

PFC 스테이지 효율

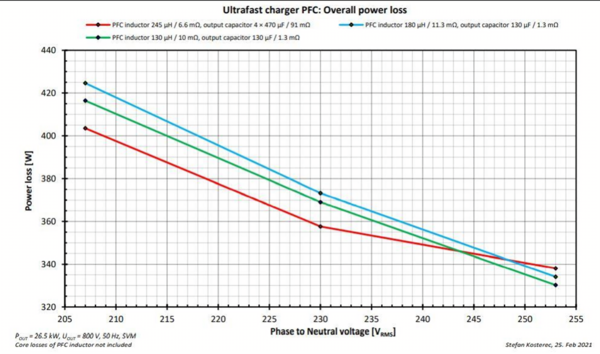

시스템 효율은 시뮬레이션의 핵심 영역이자 결과다. [그림 1]에서 [그림 3]은 효율 값과 그에 상응하는 손실을 나타낸다. 입력 전압이 높을수록 IPHASE가 감소해 전반적인 효율이 높아진다[그림 1].

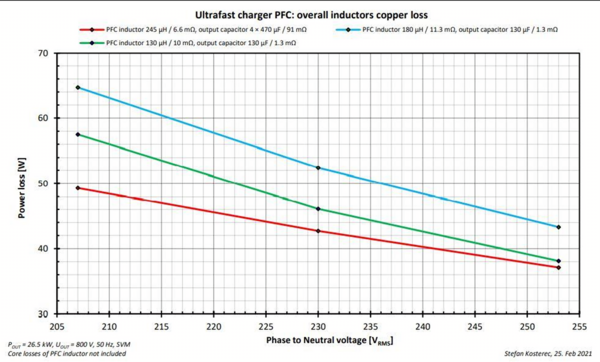

다른 인덕터를 사용하면 인덕턴스 값이 높을수록 효율이 더 좋은 것처럼 보일 수 있다. 그러나 효율에 영향을 미치는 다른 많은 요인이 있으며, 이것은 시뮬레이션이 어떻게 도움이 되는지 보여주는 예다. 계산을 통해 효율을 예측하고 다른 동작 조건에서 모든 요소를 고려하는 것은 번거로울 것이다. [그림 3]은 권선 손실에 대한 세부 정보를 제공한다. 권선 손실 간의 차이는 인덕턴스 값에 대한 총 시스템 손실 간의 차이보다 낮다.

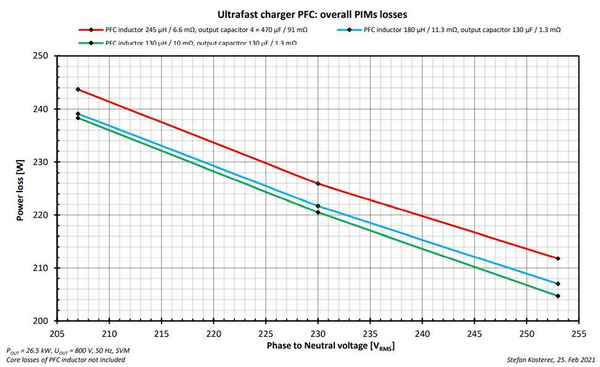

[그림 4]에서는 모듈에서 소비된 손실이 인덕턴스 값이 낮아질수록 줄어드는 것을 보여준다. 인덕턴스 값이 낮을수록 전류 리플은 높아지고, 리플이 높을수록 턴온(turn-on) 전류는 적어지므로 스위칭 손실이 감소한다.

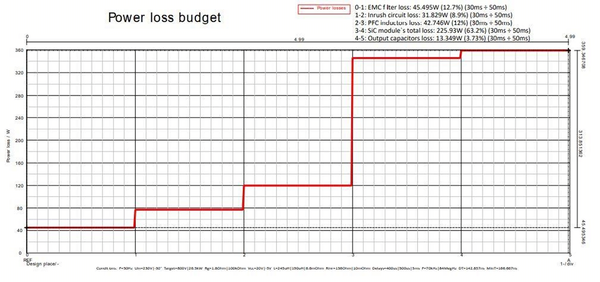

[그림 5]는 여러 요소에 걸친 손실 분포를 보여준다. 이 시뮬레이션의 주요 조건은 VIN = 230V, POUT = 26.5㎾, VOUT = 800V이며 인덕터와 커패시터 = 245µH, 4 x 470㎌이다. 시뮬레이션 시간은 50㎳이며 전력 손실 계산에 고려되는 시간대는 30 ~ 50㎳이다. 이것은 시스템이 안정적으로 동작하기 위한 시간이다.

PFC 매개변수

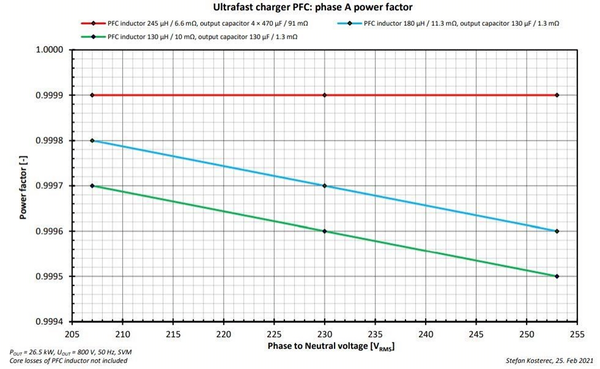

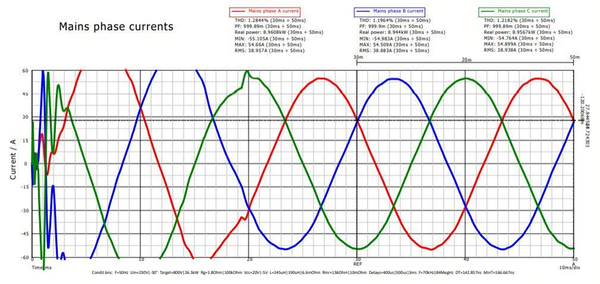

최대 부하 조건에서 0.99%를 초과하는 역률이 요구되는 전기차 고속 충전기는 역률이 핵심적인 요구 사항이다. [그림 6]은 모든 설계가 이 요구 사항을 충족하는지 확인하는 데 도움이 되며 [그림 7]은 완벽한 사인파 전류 파형과 IPHASE-VINPHASE 관계성을 보여준다.

IPHASE와 RMS값은 인덕터 값에 무관해 동일하게 유지되며, 인덕터 버전 간의 편차도 매우 작기 때문에 전체 효율 결과와 일치한다. 피크 전류에서 약간 더 큰 변동이 관측될 수 있지만 손실과 효율 추정에 사용하는 주요 전류 구성요소는 IPHASE와 RMS이므로 IPHASE와 PEAK 값은 전력 손실에 중요하지 않다. 이는 시스템 전류가 높을수록 손실이 커지는 것과 일치한다. THD(총 고조파 왜곡) 결과에서도 유사한 패턴이 나타난다.

PFC 인덕터 동작 조건

적절한 인덕터를 설계하고 선택하기 위해 입력으로 사용하는 4가지 임계 전류 값이 있다. 이 전류 값은 ▲열특성을 고려하기 위한 IPHASE와 RMS ▲인덕터 코어의 자기 포화 수준을 설명하기 위한 IPHASE와 PEAK ▲IRIPPLE와 PEAK-PEAK 코어 손실 추정 ▲권선의 절연 수준을 정의하는 VPHASE와 PEAK다.

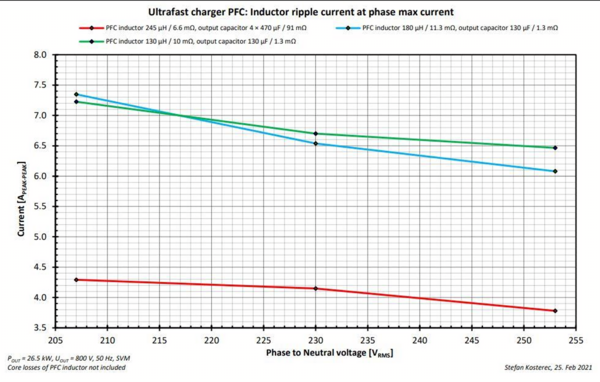

[그림 8]은 여러 VPHASE-NEUTRAL값을 기반으로 하는 인덕터의 리플 전류 피크 투 피크값을 보여준다. 245µH 인덕터는 130µH 인덕터보다 40%가량 리플이 적다. 시뮬레이션의 또 다른 세부 사항은 파형이 0을 지날 때와 피크에 있을 때 실제 IRIPPLE와 PEAK-PEAK 값이 최대값과 최소값에 도달하는 방법을 보여준다.

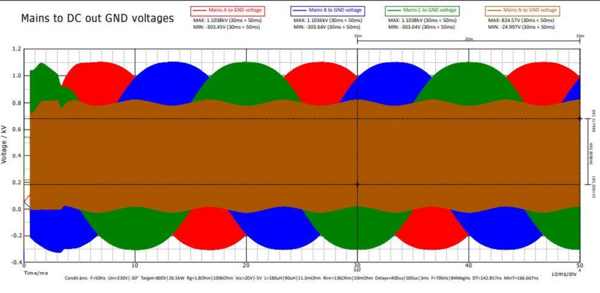

주전원과 DC 출력 간 전압

3상 PFC 시스템과 인버터에서 위상 라인, 중성선(N), 보호 접지(PE), 컨버터의 음극 DC 출력(-VDC) 사이에 전압 차가 발생한다. 이는 PFC 스테이지에서 시스템의 프론트 엔드와 백엔드 사이에 갈바닉 절연이 없기 때문이다.

[그림 9]는 입력 라인 전압과 컨버터 -VDC 사이의 전압 엔벨로프, N 또는 PE 라인과 음극 DC 출력(-VDC) 사이의 전압을 보여준다. 하드웨어 테스트와 평가 단계에서 N/PE와 -VDC 사이의 고전압은 각별한 주의와 추가 안전 조치가 필요하다. N과 PE-DC 출력 GND 전압의 엔벨로프는 그리드 주파수의 3배로 변조되는 반면 변조 깊이는 PFC 인덕터의 포화 수준에 연관된다[그림 9]. 이런 현상은 적용한 PWM 변조 방식의 영향을 받으며 여기서는 SVM 변조 시스템에서 볼 수 있는 엔벨로프에 해당한다.

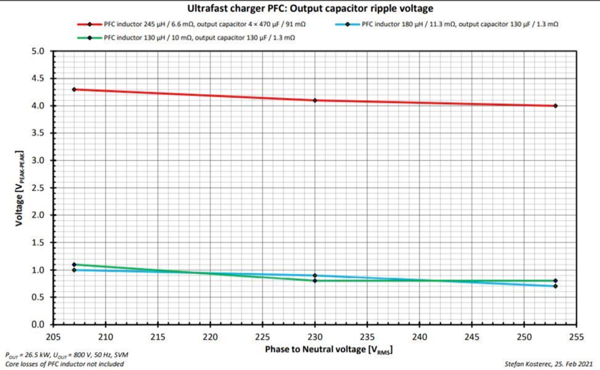

PFC 출력 커패시터

PFC 시스템의 가장 중요한 역할은 DC 링크 전압을 높이고 기준 레벨로 유지하는 것이다. PFC 출력에 배치된 DC 링크 커패시터는 이 기능을 수행해야 하며, 부하가 출력에 연결될 때 생기는 전류 리플을 효과적으로 처리해야 한다.

출력 전압 리플(VPEAK-PEAK) 값은 입력 VPHASE에 종속되지 않지만 대부분 기생 등가 직렬 저항(ESR)과 함께 DC 출력 커패시턴스의 영향을 받는다. [그림 10]은 4개의 470㎌ 커패시터를 병렬로 사용하는 4 x VPEAK-PEAK의 최악의 경우를 보여준다. 여기서 전체 커패시턴스 값은 높아졌지만 전해 커패시터의 ESR(91mΩ)이 필름 커패시터(1.3mΩ)를 비롯한 다른 커패시터보다 훨씬 높다. 출력 커패시턴스는 VPEAK-PEAK가 작고 커패시터에 대한 엄격한 홀드업 요구 사항이 없어 상당히 줄어든다.

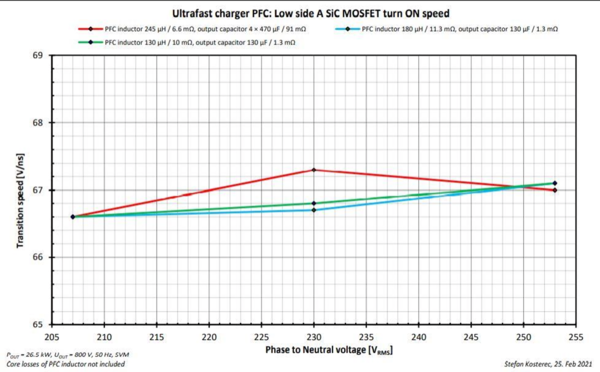

스위칭 전환: 턴온(Turn-On)과 턴오프(Turn-Off)

스위칭 전환 속도인 MOSFET의 dV/dt는 PFC 회로의 스위칭 성능을 평가하는 주요 매개변수다. 스위칭 전환이 빠를수록 손실이 적고 효율이 높다. 그러나 스위칭 속도에는 여러 제한이 있다. 빠른 전환에 의해 발생하는 높은 그라디언트와 EMI, 커먼 모드(CM) 노이즈에 대한 트랜지스터 자체의 능력 같은 것들이다.

[그림 11]은 시뮬레이션 환경에서 66V/㎱를 초과하는 dV/dt 값을 보여준다. 이런 값은 실제로 광대역 갭 기술에서만 가능한 빠른 과도 변이 현상을 나타낸다. 높은 dV/dt 값은 구성 요소에 손상을 줄 수 있으며(SiC 모듈에도 해당), 애플리케이션의 기생 인덕턴스에 의해 높은 과전압 스파이크를 생성해 최대 VDS 정격을 쉽게 초과할 수 있다.

턴온용 게이트 소스 저항 값을 수정하면 dV/dt를 줄일 수 있다. 게이트 저항 값이 높을수록 전환 속도는 느려져 애플리케이션을 더 안전하게 하지만, 추가 전력 손실이 발생한다. 시뮬레이션 결과를 기반으로 턴온 전환을 약 25V/㎱로 유지하기 위해 게이트 소스 저항의 원래 값(1.8Ω)을 2.5배(4.7Ω) 증가시켰다. 이것은 실제 하드웨어 평가에 사용되는 시작값이다.

턴오프 전환에도 유사한 접근 방식을 적용했다. [그림 12]에서 [그림 14]는 시뮬레이션에 대한 결과로 오프 트랜지션은 100kΩ 게이트 싱크 저항을 사용해 최대 40V/㎱까지 빠르게 된다. 이 저항값은 오프 트랜지션을 약 25V/ns로 조정하기 위해 증가될 예정이다.

![▲[그림 12] PFC 스테이지 MOSFET의 일반적인 턴오프 파형.](https://cdn.epnc.co.kr/news/photo/202204/221885_222620_2018.png)

![▲[그림 13] 입력 전압과 인덕터, 출력 커패시터 값의 함수로서 로우 사이드 위상 A SiC MOSFET 최대 턴오프 전류.](https://cdn.epnc.co.kr/news/photo/202204/221885_222621_2021.png)

![▲[그림 14] 입력 전압과 인덕터, 출력 커패시터 값의 함수로서 로우 사이드 위상 A SiC MOSFET 턴오프 속도.](https://cdn.epnc.co.kr/news/photo/202204/221885_222622_2025.png)

글: 캐롤 렌덱(Karol Rendek), 스테판 코스테렉(Stefan Kosterec), 디오니시스 보글리시스(Dionisis Voglitsis), 라칫 쿠마(Rachit Kumar)

자료제공: 온세미(www.onsemi.com)

그래도 삭제하시겠습니까?