6차 IEEE 반도체 패키징 학회(EPTC) 보고서(하)

Development of low profile Fan out PoP solution with embedded passive

Boo Yang Jung, David Soon Wee Ho, Dexter Velez Sorono, Sharon Pei Siang Lim,

Zhaohui Chen, Han Yong, Bu Lin and Chai Tai Chong

Institute of Microelectronics, A*STAR (Agency for Science, Technology, and Research)

11 Science Park Rd, Singapore Science Park II, Singapore 117685

Tel: (65) 6770 5428 Fax: (65) 6774 5747 Email: jungby@ime.a-star.edu.sg

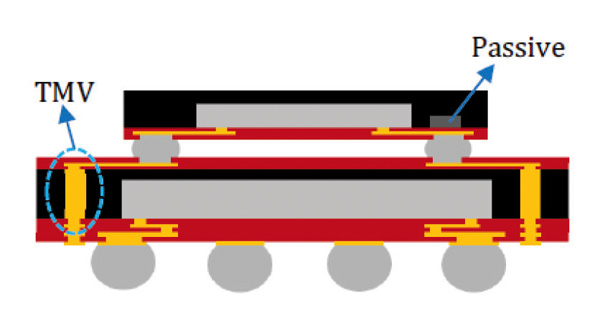

현재 PoP(Package on Package)는 모바일 기기의 베이스밴드 칩과 어플리케이션 프로세서의 핵심 패키징 기술이다. 점차 모바일 기기가 얇아짐에 따라 점차 더욱 얇은 패키지 기술이 요구되고 있는 상황에서 이를 만족시키기 위해 FO-WLP(Fan-out WLP) 기술을 이용한 초박막형 PoP 패키지 기술을 개발하였다.

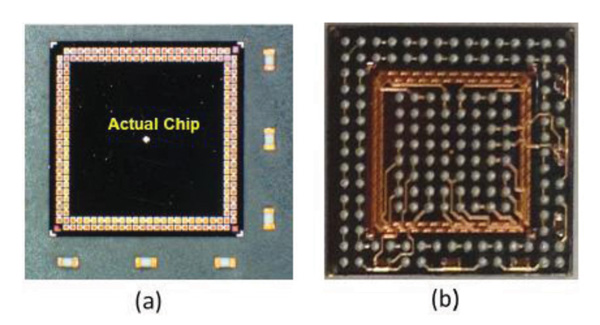

이 논문은 TMV(Through Mold Via) 기술을 통해 FO-WLP인 EMWLP(embedded wafer level CSP)에서의 3차원 적층 기술을 적용하고, PoP(package on package) 기술 개발에 관해 논의하였다.

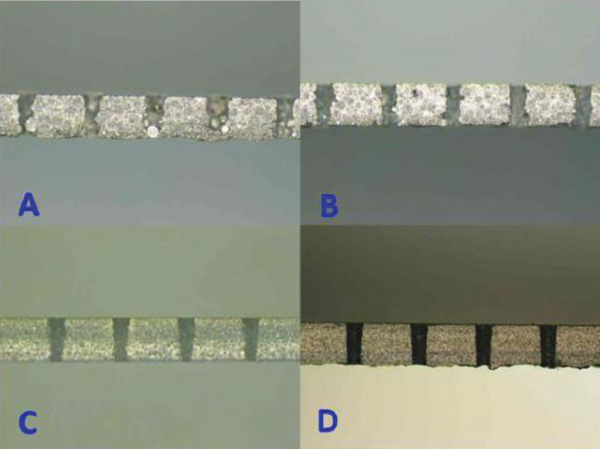

TMV이 레이저 방법을 통해 비아 홀을 만들고, 이에 구리 도금으로 비아 벽면에 전기 배선을 형성하여 위와 아래 부분을 3차원적으로 연결하는 구조를 가지게 한다. 이를 위해 2가지 공정이 필요한데, 레이저로 비아를 형성하는 공정과 구리 도금으로 비아에 3차원 배선을 형성하는 공정이다. 몰딩 콤파운드 재료는 실리카 필러(filler)와 에폭시 레진으로 구성되어 있는데, 충진 밀도를 높이기 위해 다른 크기의 필러가 존재한다.

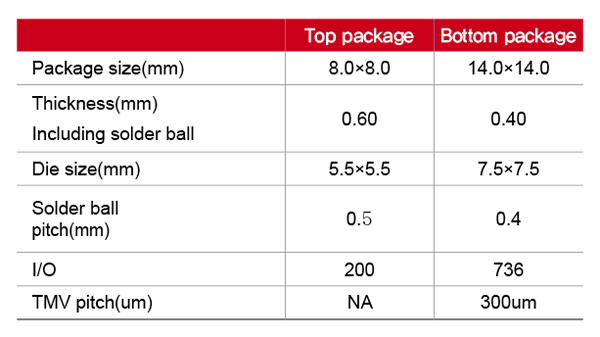

이러한 불규칙한 재료의 필러 크기 때문에 레이저로 비아를 형성할 때 불규칙한 비아 벽면이 형성되게 된다. 또한 레이저를 사용할 경우 열이 충분히 빠져나가지 않아서 구리 패드의 박리가 일어날 수 있기 때문에 패드의 디자인이 매우 중요한 역할을 하게 된다. 무전해 도금 또한 비아 표면에 균일하게 증착되기 위해서 공정 조절과 최적화가 필요하다. 표 3에 본 연구에서 제작한 시편의 상세 정보를 나타내었다.

또한 0402 수동 소자도 함께 임베딩하게 되어 이에 따른 공정 조건 확립과 패키징 완료 후의 신뢰성 테스트를 통해 패키지의 기계적 특성도 평가하였다. MSL(Moisture Sensitivity Level) 3, TC_B 1000 사이클, HTS 1000 시간 신뢰성 평가를 모두 통과함을 보고하였고, 앞으로 보드 레벨 신뢰성 테스트도 계속해서 진행할 예정이라고 발표하였다.

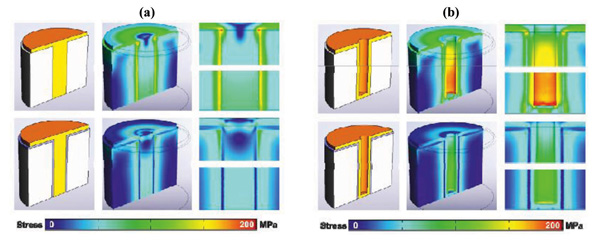

이와 같은 PoP 패키지의 경우는 패키지의 휨성이 PoP 패키지를 만들기 위해 상위, 하위 패키지를 표면 실장법(SMT)을 통해 접속시킬 때 큰 영향을 준다.

특히 패키지가 얇아질수록 그 휨성은 커지게 되므로 작업 시 양률의 손실 및 불량을 가져올 수 있기 때문에, 이에 대한 충분한 이해와 조절을 통해 원하는 스펙의 휨성을 확보하고 이후 표면 실장법 공정에서 발생할 수 있는 문제점들을 최소화시키는 노력이 패키지 개발 단계에서부터 필요하다.

앞으로 하위 패키지의 크기가 점차 커지며 또한 볼패드 피치 또한 작아지는 상황에서, 이러한 휨성과 표면 실장법 공정에 관한 이해와 충분한 연구가 반드시 선행되어야 할 것이다.

Bondability and Challenges of Cu Ultra-Fine-Wire Bonding

Sylvia Sutiono1, Zhangxi1, Tok Chee Wei1, Don Syth An1, Murali Sarangapani1

Louie Huang2, Jason Hung2, Frank Lin2

1 Heraeus Materials Singapore Pte Ltd

Block 5002, Ang Mo Kio Avenue 5, Techplace II, #04-05, Singapore 569871

Sylvia.sutiono@heraeus.com, xi.zhang@heraeus.com, cheewei.tok@heraeus.com, murali.sarangapani@heraeus.com

2 Advanced Semiconductor Engineering, INC (ASE Group Kaohsiung)

26, Chin 3rd Rd, Nantze Export Processing Zone, Kaohsiung Taiwan 811, R.O.C

Louie_Huang@aseglobal.com, Jason_Hung@aseglobal.com, Frank_Lin@aseglobal.com

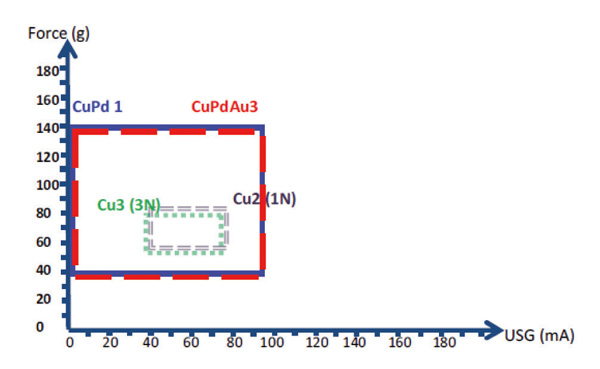

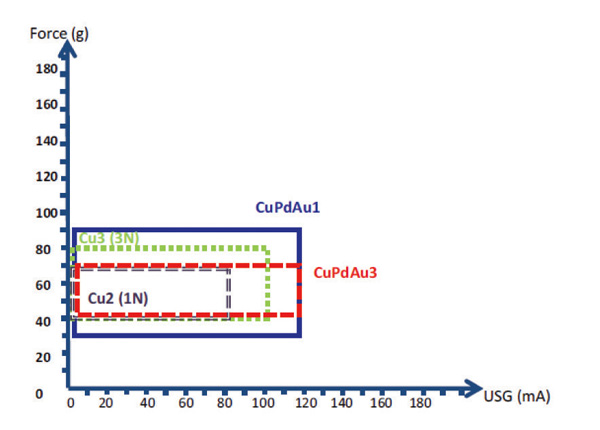

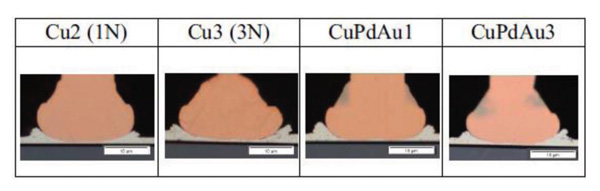

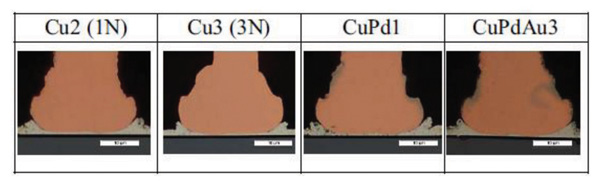

이 논문은 구리 와이어 본딩에서 매우 미세한 0.5/0.6mil의 두께를 가지는 Cu, CuPd 그리고 CuPdAu 와이어를 이용하여 30um 미세 패드 피치에서의 작업성과 공정을 보고한 논문이다.

미세한 와이어 본딩에서 중요한 당김, 밈 응력 테스트 및 작업 공정 윈도우 등의 특성에서 CuPd의 경우 2차 본딩 특성이 매우 훌륭했으며, Cu의 경우는 1차 본딩 특성이 우수함으로 보고하였다.

와이어의 직경이 작아짐에 따라 와이어 볼을 형성하는 에너지도 따라 작아지게 된다. EFO (electronic flame off) 전류값, Firing 시간 등 작업 조건들도 점차 미세하게 조절하여야 한다.

구리의 경우는 금과 비교하여 더욱 강하기 때문에 쉽게 변형되지 않는다. 이미 골드 와이어를 사용하여 30um 패드 피치에서의 작업성은 확보되었으나, 강성의 와이어를 가지는 구리의 경우는 알루미늄 패드의 스플래시를 어떻게 적게 가지고 갈 것인가가 첫 번째 도전이다.

그림 22, 23에서 보인 바와 같이 0.5mil을 사용하였을 경우에 더 많은 플래시를 보여주고 있다. 특히 이러한 플래시는 미세 피치의 경우 옆에 발생한 플래시에 맞닿아서 전기적 short를 가져올 수가 있다. 0.5mil의 경우는 작은 와이어 볼과 알루미늄 패드 스플래시, 특히 Y축으로 발생하는 스플래시를 조절하여야 하는 어려움이 있다.

현재 0.7mil Cu/CuPd를 사용하여 양산 중에 있으나 앞으로 0.6/0.5mil을 양산에 적용하는 데는 좀 더 시간이 필요할 것으로 생각한다. 와이어가 얇아짐에 따른 경제적 효과가 없으며 또한

요구하는 분야도 한정적이기 때문에, 좀 더 시간을 두고 본딩의 품질 문제와 시간, 힘과 같은 다른 제어 공정 작업 변수에 대한 연구가 충분히 있어야 할 것이다.

Study on Electrical Characteristics for Active Die Embedding Substrate

Hyunho Kim

Center for Integrated Smart Sensors

#313 ITC Building (N1), KAIST, 291 Daehak-Ro, Yuseong-Gu, Daejeon, Korea

kimmrl1022@kaist.ac.kr

이 논문은 수동 소자 임베딩 기판 기술에서의 전기적 특성과 신뢰성을 평가한 결과에 대한 발표이다. PCB(Printed Circuit Board: 인쇄회로 기판)는 여러 종류의 부품을 페놀수지 또는 에폭시 수지로 된 평판 위에 탑재하고 각 부품 간을 연결하는 회로를 수지 평판의 표면에 밀집, 단축하여 고정시킨 회로 기판으로, 모든 전자 제품의 근간을 이루는 핵심 부품이다.

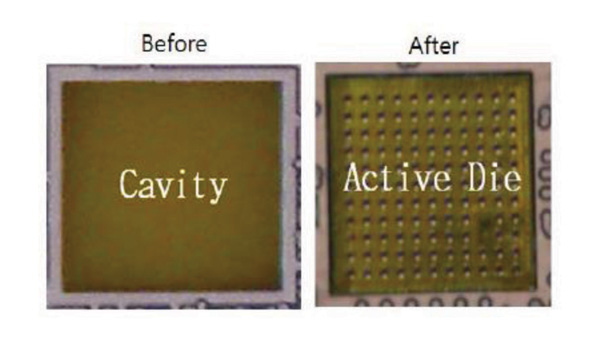

▲ 그림 30. 임베딩 기판에 캐비티를 형성하고

그 안에 수동 소자(반도체 다이)를 삽입한 후의 모습

최근엔 디지털 네트워크 정보사회의 급속한 진전에 따라 모바일 정보 단말에서 고성능·고기능화(복합화, 융합화), 소형화 그리고 정보처리 속도의 가속화 등의 기능이 요구되고 있다. 특히 전자 기기의 소형화에 따른 제조 기술의 변화 요구에 대응하는 소형화 기술의 선택은 비즈니스의 중요한 변수로 각광받고 있다.

이처럼 소형화가 중시됨에 따라 다수의 부품(Passive 및 Active)을 다층 기판 내에 내장함으로써 부품의 실장 밀도를 획기적으로 증가시키고, 점차 능동 소자인 IC도 매립되는 기술이 적용되어 로직, 메모리와 아날로그 등 다양한 소자의 융합 및 파워 감소 측면에서도 장점이 있다.

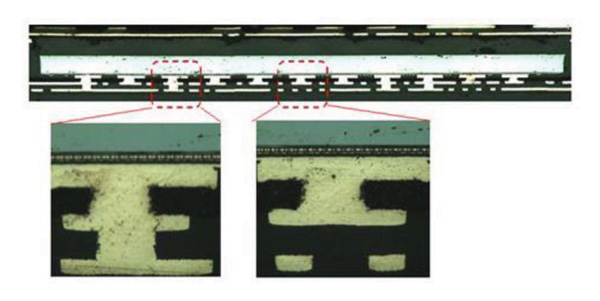

▲ 그림 31. 그림 17의 공정 후 기판 공정을 통해 구리 배선을

형성한 후의 단면 미세구조

이 논문에서는 고성능·다기능화 구현을 위해 인쇄회로 기판상의 능동·수동 부품 수가 늘어남으로 인해 일어나는 기판의 면적 증가를 줄이기 위해, 큰 면적을 차지하는 능동 소자인 칩을 기판 내부에 내장(Embedding)하고, IC가 내장된 기판 표면에 수동 부품의 표면 실장 방식으로 모듈의 크기를 소형화(기존 대비 >50%)할 수 있는 기술을 제공할 수 있다.

기판 내부에 반도체 소자를 내장하게 되면 공간적으로 많은 영역을 확보할 수 있기 때문에 모듈이나 SiP와 같은 패키징에 효과적이다.

본 연구에서는 4×4~6×6mm 크기의 다이를 그림 17과 같은 기판 캐비티 내에 삽입한 후 기판 제조 기술을 이용, 다층의 배선을 형성한 후 최종 다이싱을 통해 패지지를 구현하였다.

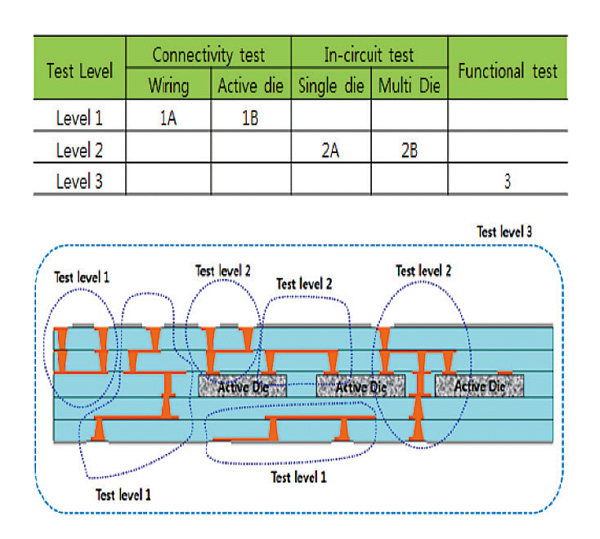

이후 전기적 특성을 측정하기 위해 Level 1~3에 해당하는 테스트를 실시하였고, 또한 신뢰성을 알아보기 위해 TC-B 조건 -55/+125C의 온도 사이클링 시험에서 1000 사이클 실험을 하였다.

능동 소자 임베딩 기판 기술은 10여 년이 넘는 개발 역사를 가지고 있는 패키징 기술이다. 많은 연구와 개발이 이루어지고 있으며, 일부 모듈 및 PCB 기판의 양산을 시작하였다. 하지만 아직 메인 스트림 패키징 기술로 자리를 잡고 있지 못한데, 이는 기판이 가지고 있는 양품율(yield)이 큰 문제가 되기 때문이다. 패키지의 경우 조립 생산 양품률은 99.9% 이상이다. 하지만 기판의 경우 95%를 넘기가 힘들다.

따라서 대량생산과 큰 패널을 사용함에서 오는 제조 가격 인하의 효과가 크지만 그만큼 불량이 많이 생기기 때문에 KGD(Known Good Die)의 손실이 오게 된다. 따라서 다이의 단가가 낮은 소자나 수동 부품 등은 보다 쉽게 접근할 수 있어 현재 양산은 대부분 이러한 제품들에 대해 이루어지고 있는 실정이다. 따라서 이러한 양품률을 높이는 공정 개발과 안정성 방향으로 보다 많은 개발과 연구가 이루어져야 할 것으로 생각한다.

Innovative Wafer Level Package Manufacturing with FlexLine

Kang Chen, Kok Hwa Lim, Kenneth Seah, Yaojian Lin

STATS ChipPAC Ltd. 5 Yishun Street 23, Singapore 768442

chenkang@statschippac.com

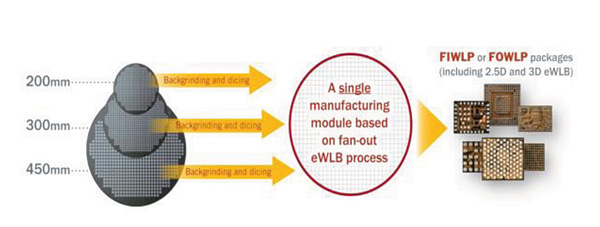

이 논문은 최근 각광받는 임베딩 패키지 기술의 하나인 Fan-out WLP(wafer level packaging)에 대한 내용이다. 특히 Fan-out WLP의 하나인 eWLB(embedded Wafer Level Ball Grid Array)와 이 공정을 이용한 eWLCSPTM(encapsulated Wafer Level Chip Scale Package)를 하나의 생산 라인에서 하나의 동일한 재료들을 사용해서 생산해내는 FlexLineTM 플랫폼 패키징 기술에 관해 발표하였다.

▲ 그림 34. FlexLineTM 기본 개념도. 웨이퍼 크기에 관계없이

FI-WLP/FO-WLP를 생산해낼 수 있는 생산 공정 기술

Fan-out WLP(FO-WLP)의 경우는 재구성(reconstitution)이라는 공정을 통해 인공 웨이퍼를 형성한다. 따라서 초기 fab-out된 웨이퍼가 6, 8인치 또는 12인치가 되어도 제조 공정상에는 큰 문제가 없다. 이러한 이점 때문에 하나의 생산 라인을 통해 Fan-in/ Fan-out WLP를 생산해낼 수 있는 장점이 있다.

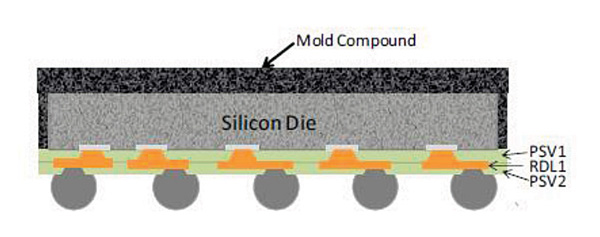

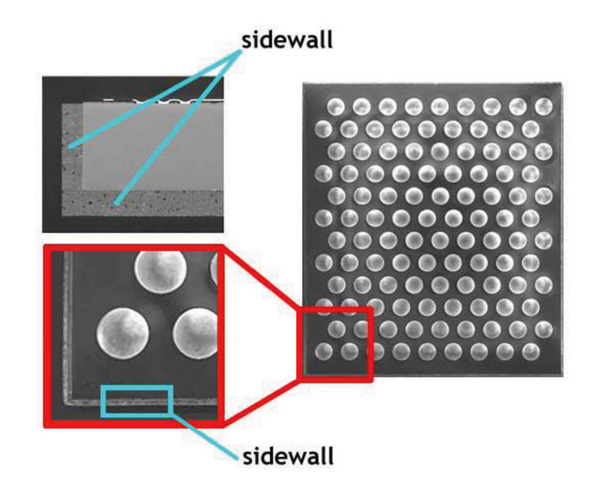

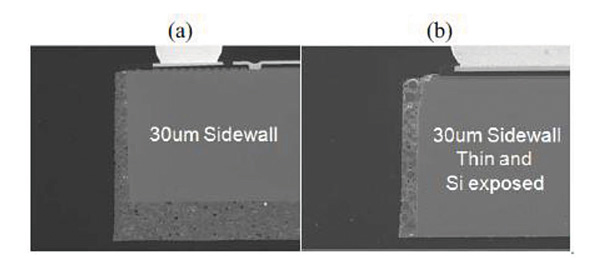

eWLCSPTM의 경우 칩과 패키지 사이에 30um 정도의 간격이 존재하고, 여기에 플라스틱 레진이 채워져 노출된 실리콘 벽면을 보호할 수 있다. 이로 인해 발생하던 칩 크랙 등 기계적·물리적 손상부가 보호되고, 나아가 신뢰성 측면에서도 효과적이다.

또한 기존의 FI-WLP가 가지는 문제점인 양품률 문제도 해결 가능하다. 웨이퍼의 양품률이 80%이면 패키징이 끝난 후에 20%는 못 쓰게 되어 결국 버려지는 20%의 손실로 실제적으로 가격이 높아지는 현상이 발생한다.

하지만 앞에서 언급한 재구성 공정을 사용하면 KGD만 골라서 인공 웨이퍼를 형성할 수 있기 때문에 보다 효과적으로 패키징을 실현할 수 있어 전체 가격을 낮출 수 있는 장점이 있다.

eWLCSPTM는 기존의 WLCSP와 같은 기능, 모양과 크기에 있어 동일하지만 FlexLineTM 플랫폼을 통해 대량생산 시 더욱 저렴하고 또한 신뢰성을 향상시키는 패키지 구조를 가지는 장점이 있다.

▲ 그림 37. eWLCSPTM SEM 단면 사진.

(a) 5-side protection and (b) 박막형 패키지.

본 논문에서는 JEDEC 단품 신뢰성 실험과 보드 실장 시험을 모두 패스함을 보고하였다.

또한 eWLB/eWLCSPTM 인공 웨이퍼 상태에서 최종 테스트를 마칠 수 있는 공정을 개발하여 이를 통해 FI-WLP와 동일한 패키징 및 테스트 공정 흐름을 가져갈 수 있다. 이를 위해 필요한 부분에 일부 파트와 구조에 업그레이드가 이루어졌다. 특히 재구성 후 인공 웨이퍼는 휨성을 가지고 있기 때문에 거의 평평한 FI-WLP에 비해 핸들링과 고정하는 부분 등에 새로운 개발이 필요하였다.

이러한 부분들을 수정한 후 최종적으로 eWLB 웨이퍼 최종 테스트를 완성하였다.

이러한 새로운 웨이퍼 레벨 패키징 기술은 기존의 반도체 공정의 일부를 사용하기 때문에 기존 반도체 공정과 연속성을 가지고 있어 최신 반도체 노드 기술의 CPI(chip-package-interaction) 개발에 보다 효과적이다. 또한 기존 플립칩 패키지가 가지는 기계적인 문제점들을 쉽게 극복할 수 있으며, 그 특성도 보다 향상되는 것으로 보고되었다.

앞으로 이와 같은 기술들이 많이 양산으로 확대될 것으로 전망하며, 기존의 반도체 패러다임에서 새로운 와해성 기술(destructive technology), 또는 혁신(innovation) 기술들이 많이 일어날 것으로 예상된다.

W2W Permanent Stacking for 3D System Integration

Lan Peng1*, Soon-Wook Kim1, Michael Soules2, Markus Gabriel2, Margarete Zoberbier2, Erik Sleeckx1,Herbert Struyf1, Andy Miller1, Eric Beyne1

1 IMEC, Kapeldreef 75, 3001 Heverlee, Belgium

2 SUSS MicroTec, Schleissheimer Strasse 90, 85748 Garching, Germany

*Corresponding Author; email: lan.peng@imec.be ; Tel: (32)-1628-3304

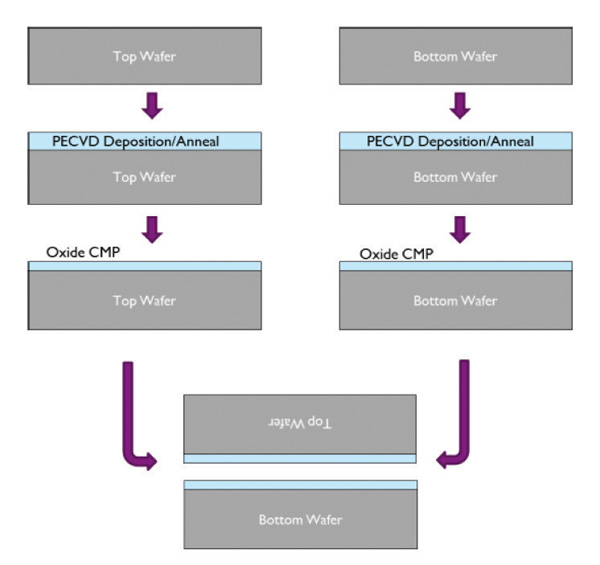

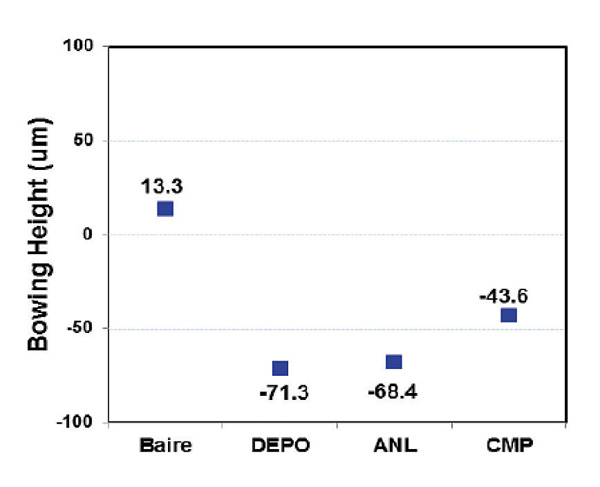

이 논문은 웨이퍼-웨이퍼 본딩을 통해 TSV 웨이퍼를 적층하는 공정에 관련된 것이다. 특히 실리콘 산화막을 이용하여 이를 이온결합과 공유결합을 통해 접합시켜 완전한 본딩을 형성하는 방법으로, 온도와 압력 그리고 분위기의 조절을 통해 기공과 불량이 없는 본딩을 이루었다.

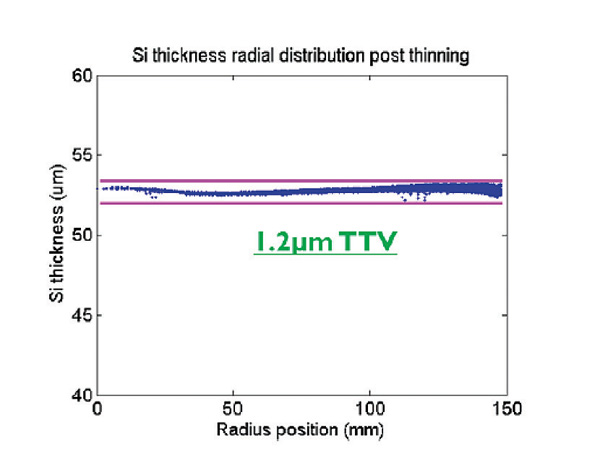

특히 화학적 세척 공정과 플라즈마 공정을 선처리하여 CMP 후의 각 산화막 표면을 활성화시켜 이들이 충분한 반응으로 접합이 일어날 수 있도록 노력하였다. 이를 SAT(Scanning Acoustic Termography)를 이용해 확인하였고, 또한 높은 본딩 균일도를 보임도 확인하였다. 특히 본딩한 웨이퍼를 다시 갈아서 얇게 만드는 그라인딩 공정 후에도 1.2um의 TTV(total thickness variation)을 보여주었다.

하지만 본 연구에서는 실제 소자 웨이퍼가 아닌 테스트 웨이퍼를 사용하였기 때문에 웨이퍼상의 토폴로지나 요철 등에 대한 문제점이 상대적으로 없었을 것으로 예상하고, 실제의 경우에는 좀 더 실질적인 문제가 있어 이에 대한 극복 방안과 연구가 있어야 할 것이다. 특히 본딩 패드의 피치가 더욱 미세화됨에 따라 본딩 시 위치의 정확성 그리고 본딩 후 웨이퍼의 품질을 확인하기 위한 새로운 양산용 장비 등이 요구된다.

지난 10년간 긴 전기 배선의 길이를 줄이고자 하는 웨이퍼 레벨의 3차원 회로 집적에 대한 개념은 집적회로의 성능 향상을 위해 제안되었다. 그 개념을 달성하려는 기술로서 내장형 박막 트랜지스터(embedded thin film transistors, TFTs)나 웨이퍼 본딩을 이용해 웨이퍼들을 적층한 후 그 웨이퍼들을 내부적으로 연결시키기 위해 비아를 이용하는 방법이 주로 고려되었다.

▲ 그림 40. W2W 본딩한 웨이퍼를 백그라인딩하여

얇게 만든 후의 TTV(Total Thickness Variation)

한편, 본딩 매개체로서 구리, 솔더 등의 금속, 저유전체 고분자 수지, 실리콘 산화물을 이용하는 웨이퍼 본딩 기술들이 웨이퍼 간 전기 배선 연결을 위해 수마이크론 크기의 비아를 형성하는 기술과 더불어 개발되고 있다. 이러한 W2W 본딩 기술은 적층 메모리 등 3D TSV뿐만 아니라 MEMS, CIS, LED 등의 다양한 분양에 적용 가능하며, 앞으로 그 반도체 외에도 활용 범위를 넓혀갈 것으로 생각한다.

결론(학회 총평)

이번 EPTC 2014 학회에서는 현재의 양산 제품 기술의 혁신 그리고 새로운 패러다임으로 앞으로 다가올 미세 피치, 고기능화, 소형화에 초점이 맞춰져 있었다. 특히 웨이퍼 레벨 패키징과 2.5D 3D TSV 및 3차원 패키징 기술을 이용한 다양한 형태의 SiP 기술 제조, 새로운 플립칩 기판을 이용한 기술 등의 논문들이 발표되었다.

현재 세계 반도체 생산과 전자 패키징의 중심 세력으로 아시아가 부상하고 있는 상황으로, 이번 학회에서는 중국과 동남아시아(말레이시아, 태국, 필리핀, 싱가포르)에서 많은 논문들이 발표되어 다양한 패키징 생산 관련 기술의 현황과 새로운 기술 개발이 많이 소개되었다.

특히 많은 중국 산업체, 연구소, 대학 등에서 참석하여 중국 시장과 중국 파워를 실감할 수 있었으며, 유럽 및 다국적 업체들의 발표를 통해 새로운 응용과 기술이 어떻게 새로운 반도체 패키징과 소자에 적용되는지에 관해 실용적인 면과 학문적인 면 양 측면에서 모두 충실한 접근이 이루어졌다고 생각한다.

또한 그림 42와 같이 사물인터넷, 센서 제품 및 착용형 전자 제품 등이 차세대 제품군으로 성장할 것으로 예측하며, 이를 준비하고 필요한 기술 개발 방향에 대한 논의가 특히 많이 이루어졌다.

하지만 아직 개념적이고 피상적인 차원에서만 논의가 이루어지고 있어 앞으로 구체적이고 현실적인 액션 아이템들이 필요한 상황이다.

결론적으로 이번 EPTC 2014 학회에서는 기존 패키징이 가진 부품 레벨의 개념적 범위가 점차 광범위해지면서 보다 다양한 접근 방법으로 기존의 패키징 기술과 새로운 기술의 혼합을 꾀하고, 경박단소화와 다양한 기능의 여러 칩들을 패키징을 통해 일체화하려는 노력이 많이 엿보였다. 또한 경제적인 면에서도 최대의 효과를 내기 위해 많은 노력과 개발이 있음을 볼 수 있었다.

▲ 그림 42. 착용형 컴퓨터 및 바이오 센서 제품들

(source: CK Lim, IMPACT 2014, Keynote speech, Taiwan, Oct 2014)

웨이퍼 레벨 패키지가 10여 년 전에 소개되어 현재 휴대폰, 스마트폰, 태블릿 등의 휴대용 소형화 제품에 많이 사용되고 있으며, 앞으로 사물인터넷, 스마트 센서, 스마트 안경, 스마트 시계 등 착용형 제품에 더욱 긴요한 제품 기술도 적용될 것으로 생각된다.

또한 웨이퍼 레벨 패키지뿐만 아니라 TSV를 통한 2.5D 인터포저 패키지 기술과 이를 보완하는 FO-WLP 기술에 대한 관심이 커지고 있어, 이를 응용한 패키지 기술과 적용 분야 대해 많은 관심이 쏠리고 있다.

앞으로 IoT와 착용형 전자 제품 그리고 나아가 자동차용 전자 시스템, 로봇 등 새로운 분야에 대한 기술적 요구와 경제적 요구가 거세질 것으로 생각하며, 차세대 반도체 전자 부품의 응용 분야로 급부상할 것이다.

따라서 이에 적합한 재료 및 제품 기술 개발과 경쟁력 있고 대량생산이 용이한 기술들이 준비되어야 할 것이다.

그래도 삭제하시겠습니까?