[테크월드=선연수 기자] 지난 6월 에릭슨(Ericsson)은 모빌리티 보고서를 통해 NB-IoT, Cat-M를 포함한 매시브(Massive, 대규모) IoT의 배포는 전 세계적으로 계속되고 있다고 밝혔다. 코로나19로 인한 배송 문제로 예상보다는 더딘 상황이다. 현재 대부분의 IoT 애플리케이션은 여전히 2G, 3G 기술로 연결되고 있다.

급증하는 매시브 IoT

2019년 매시브 IoT 애플리케이션 수는 전년 대비 3배 늘어났으며, 올해 말에는 약 1억 개에 달할 것으로 전망된다. 에릭슨은 2025년 말 NB-IoT와 Cat-M가 모든 셀룰러 IoT 장치의 52%를 차지할 것으로 예측했다. 아시아 지역의 성장 속도가 가장 빠를 것이며, 2026년 전에 전체 출하량의 67%를 점유할 것으로 예상된다.

3GPP 표준 상황도 알아보자. 릴리즈 15(Release 15)는 NB-IoT와 Cat-M에 관계없이 안정성과 애플리케이션 분야를 강화했다. 지난 7월 3일 고정된 릴리즈 16(Release 16)은 네트워크 효율성을 더 높이고 5G 환경에서 작동할 수 있는 최신 NB-IoT의 배치를 지원할 것이다. 릴리즈 17(Release 17)은 대역폭 어그리게이션(Aggregation, 집계)과 지연 시간을 낮춘 성능을 더 확장함으로써, 5G NR에 기반한 셀룰러 IoT 활용 범위를 넓힐 잠재력을 가진 애플리케이션을 개발·탐색한다.

IoT를 위해 움직이는 기업들

IoT 애플리케이션이 시장에서 널리 채택되기 위해서는 저비용, 낮은 전력 소비, 컴퓨팅 효율성 등 다양한 설계 사항을 충족해야 한다. 특히, 스마트스피커나 스마트미터와 같은 배터리 구동 장치는 다양한 IoT 기능, 손쉬운 인터페이스뿐만 아니라 배터리 수명도 제품 성공의 열쇠가 된다. 이로 인해 저전력 성능은 더 중요해지고 있다. 긴 배터리 수명을 위해서는 이를 고려한 MCU 제품을 사용하고 주변 부품 또한 저전력 성능을 따져봐야 한다.

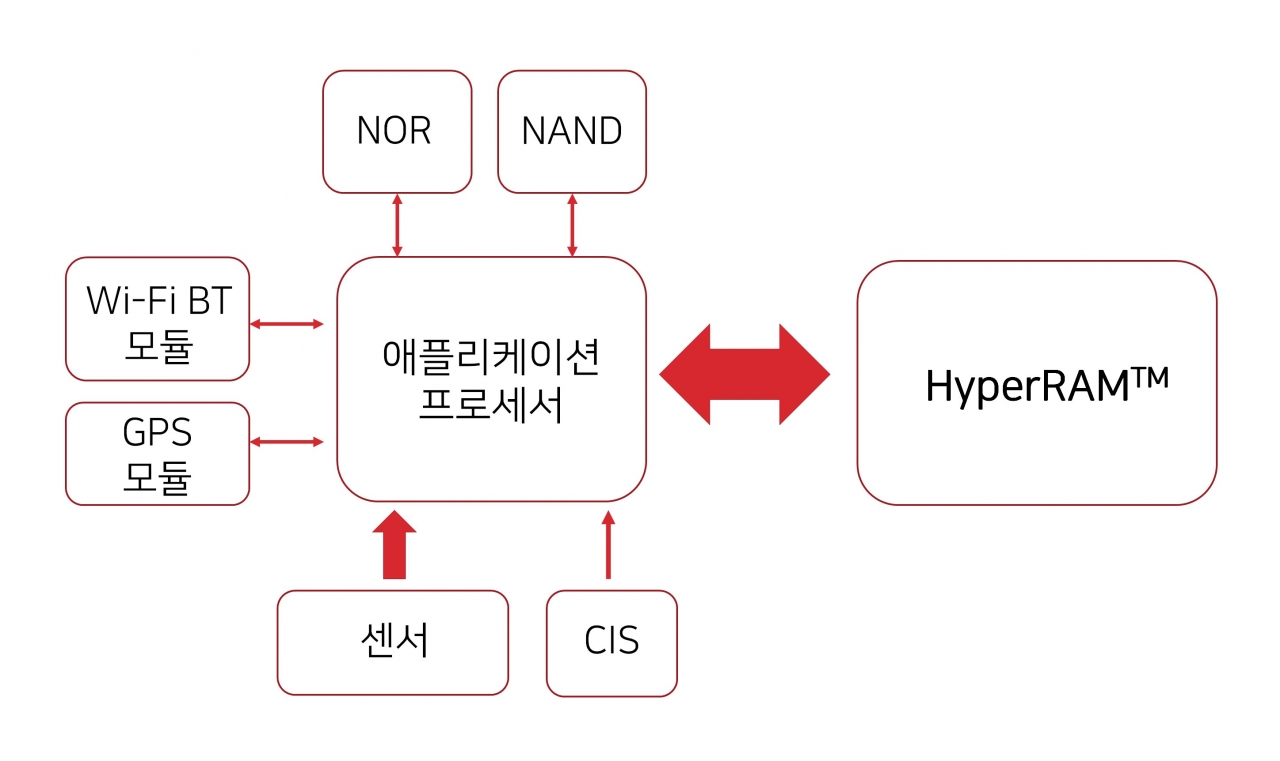

많은 모바일 장치는 [그림 1]과 유사한 아키텍처를 갖는다. 이런 블록 다이어그램은 태블릿이나 스마트워치에서 주로 나타난다. 하나씩 살펴보면, Wi-Fi·BT와 셀룰러 모듈은 통신을 담당한다. 터치 패널과 같은 센서는 외부에서 정보를 수집하고, 이를 애플리케이션 프로세서로 전달하는 역할을 맡는다. NOR과 낸드(NAND)는 D램이 임시 처리하는 동안 코드와 데이터를 저장한다.

많은 MCU 공급 업체가 앞서 말한 것들을 고려해 더 높은 성능의 더 낮은 소비 전력을 갖는 차세대 MCU를 개발하고 있다. 전체 시스템 설계 관점에서 볼 때, MCU와 함께 작동하는 D램은 기존의 SD램, 저전력 SD램, C램/PS램보다 더 우수한 성능의 새로운 옵션이 요구되고 있다. 그러나 이런 D램의 표준은 이미 오래전에 정의됐기에 [표 1]과 같은 최신 기술을 발맞춰 따라갈 수 없었다.

하이퍼버스(HyperBus) 인터페이스를 지원하는 하이퍼램(HyperRAM)은 이런 요구 사항을 다루는 최신 솔루션이다. 하이퍼버스 기술은 2014년 싸이프러스(Cypress)가 처음 공개한 기술로, 2015년 첫 하이퍼램 제품이 출시됐다. 윈본드 일렉트로닉스(Winbond Electronics, 이하 윈본드)는 시장 수요를 고려해 하이퍼램 캠프에 참여를 결정하고, 32Mb·64Mb·128Mb 밀도의 제품을 출시했다.

하이퍼램의 장점

하이퍼램은 단 13개의 신호 IO 핀을 가지며, 이를 통해 PCB 레이아웃 설계를 크게 간소화할 수 있다. 이는 최종 단계의 제품 설계 시 MCU가 핀 아웃을 다른 용도로 많이 활용할 수 있도록 하거나 더 적은 핀을 사용해 비용 효율성을 높일 수 있도록 돕는다.

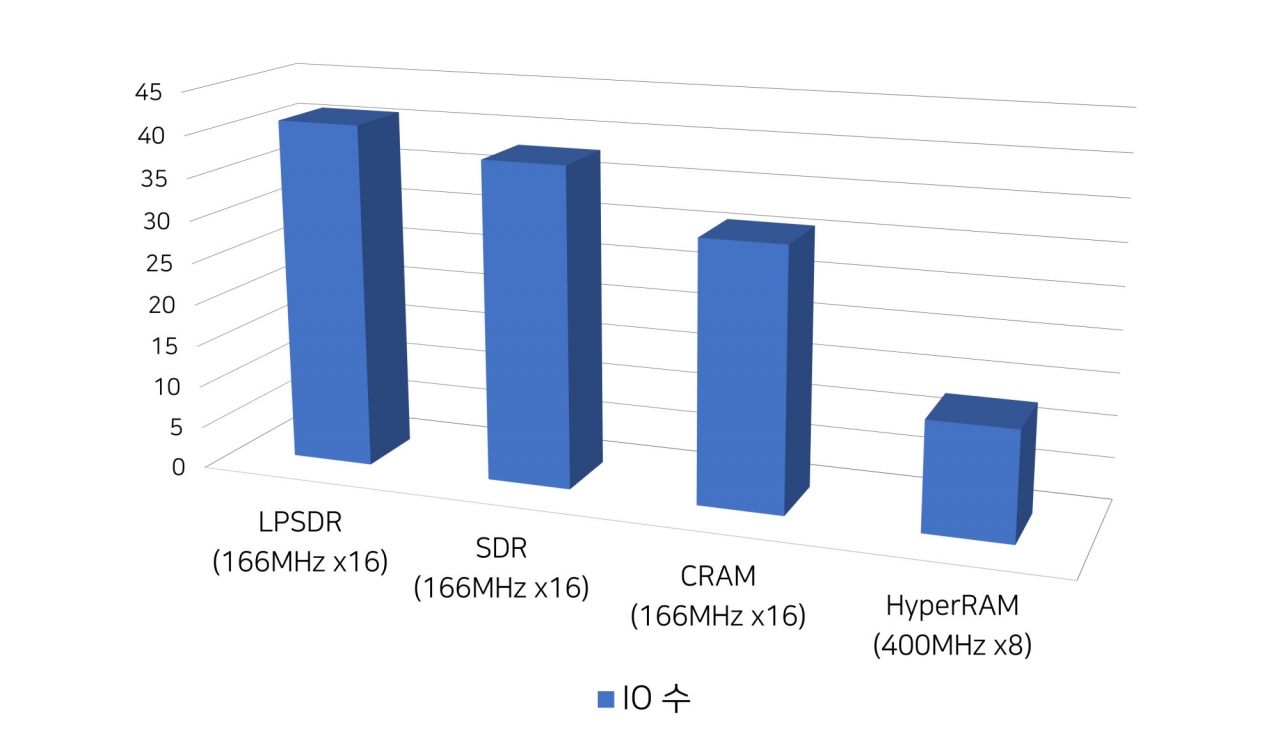

[그림 2]에서 보는 것과 같이 하이퍼램은 거의 비슷한 스루풋(333MB/s)을 달성하기 위해 저전력 D램, SD램, C램/PS램 등의 D램보다 더 적은 핀 수만으로도 충분하다.

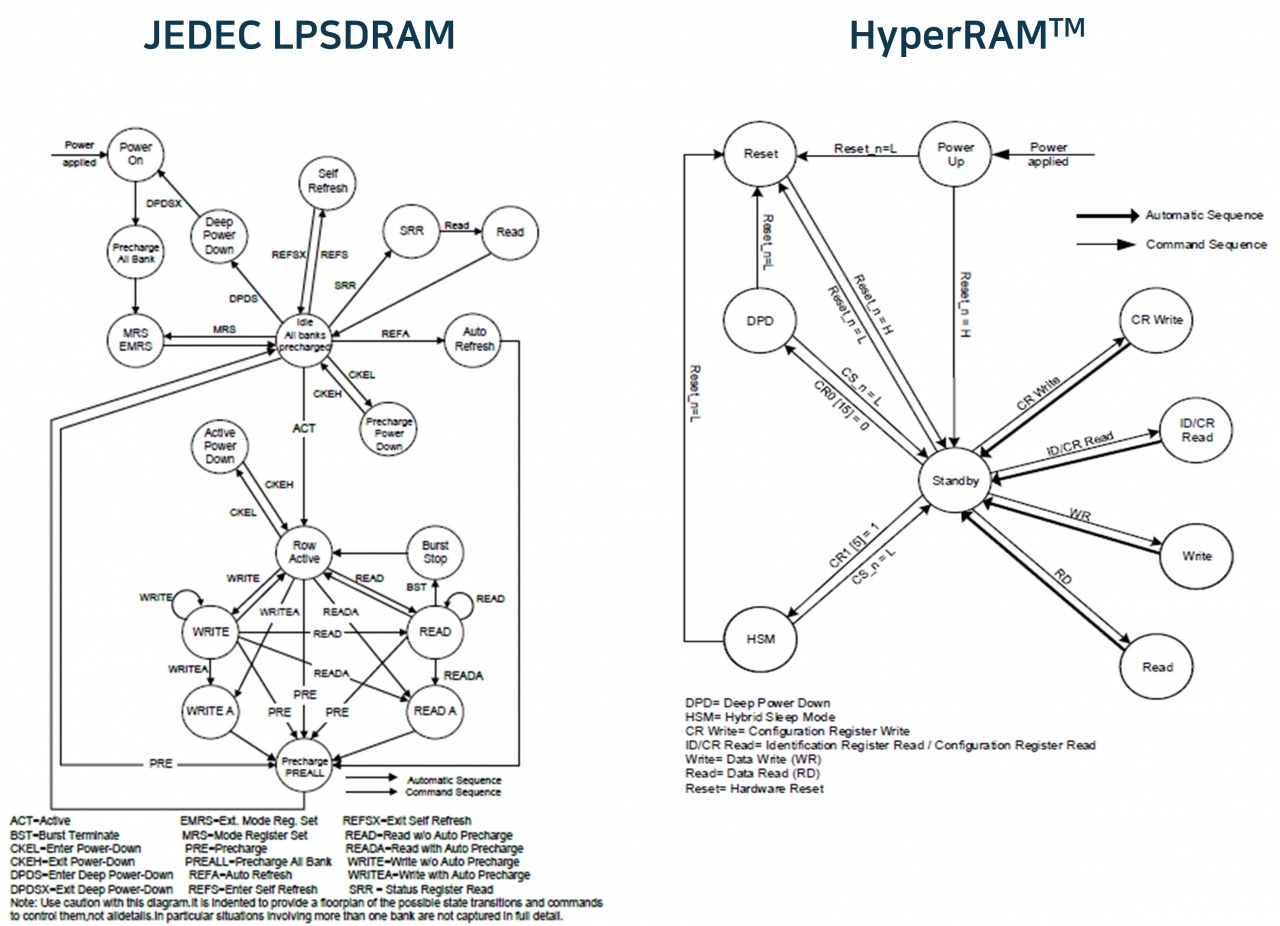

하이퍼램의 또 다른 특징은 제어 인터페이스를 간소화해주는 점이다. LPSD램 18개가 드는 곳엔 PS램은 9개만 있으면 된다. 플로우 상태(Flow state)가 더 적을수록 D램 제어가 덜 복잡해지기 때문이다. 자세한 차이는 [그림 3]을 통해 확인할 수 있다.

예를 들어, PS램 아키텍처에 기반한 하이퍼램은 셀프-리프레시(Self-refresh, 스스로 초기화되는) 램이다. 게다가, 자동으로 대기 모드로 돌아갈 수 있어 시스템 메모리를 더 쉽게 사용하도록 해주며, 펌웨어와 드라이버 개발 복잡성도 덜어준다.

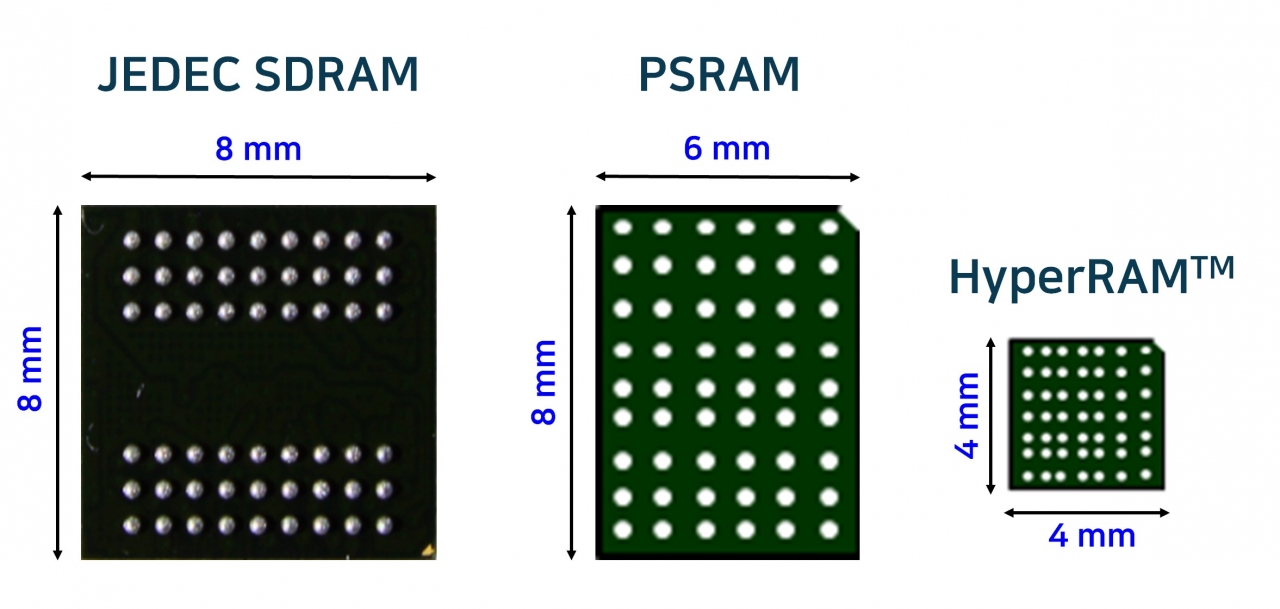

하이퍼램은 최신 반도체 공정 노드와 패키지 기술로 개발돼, 다른 D램보다 패키지 크기가 더 작다. [그림 4]는 JEDEC, PS램, 하이퍼램에서 정의된 SD램의 크기를 비교한 것이다.

전력 소모 성능 비교

IoT 장치는 보통 배터리로 전원을 공급하기 때문에 전력 소모 성능이 중요하다. 소비되는 전력을 줄이는 것은 사용 에너지를 아낄 뿐 아니라 교체·대체 비용도 절감해준다.

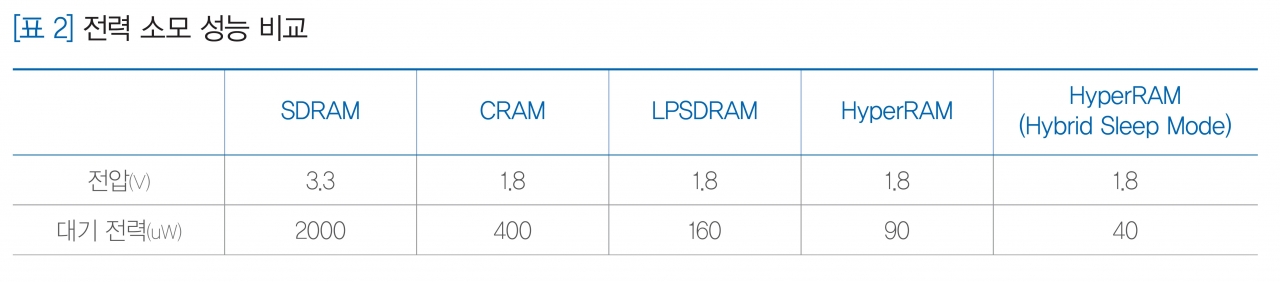

윈본드의 64Mb 하이퍼램을 예로 들면, 대기(Standby) 모드의 전력 소비는 90uW, 1.8V이지만, 같은 캐패시티(용량)의 SD램은 약 2000uW, 3.3V다. 더 중요한 것은 하이퍼램의 전력 소모는 하이브리드 슬립 모드(Hybrid Sleep Mode)에서 오직 45uW, 1.8V였고, 이는 SD램의 대기 모드에서와 상당한 차이를 보인다[표 2]. 저전력 SD램의 경우에도 전력 소모와 폼팩터 모두 하이퍼램보다 크다.

하이퍼램 기업 생태계

기존에 쓰이던 SD램과 PS램은 이미 성숙한 기술로, 새로운 IoT 애플리케이션에 최적화하기엔 어려움이 있다. 오토모티브와 산업용 애플리케이션 제품에 요구되는 장기적인 공급 사항을 고려해볼 때, 윈본드 하이퍼램의 고급 공정 노드는 제품의 긴 수명 주기를 충족할 수 있다.

전체 시스템 설계와 제품 수명의 관점에서 하이퍼램은 최신 IoT 장치를 지원할 수 있는 적합한 선택이다. 싸이프러스 외에도 NXP 반도체, 르네사스, ST마이크로일렉트로닉스, 텍사스 인스트루먼트(TI)와 같은 MCU 선도 기업들은 이미 하이퍼버스 인터페이스를 지원하는 MCU를 제공하고 있다. 이런 지원은 신제품에도 계속 적용될 것이다.

제어 인터페이스의 개발 플랫폼도 준비돼 있다. 케이던스(Cadence)와 시놉시스(Synopsys)도 하이퍼램 메모리 검증 IP(memory verification IP)를 제공하기 시작했다. 이 솔루션을 다른 옥탈 램(Octal RAM)과 비교해보면, 하이퍼램이 가장 고도화된 애플리케이션 환경을 가진다는 것을 알 수 있다. 하이퍼램은 JEDEC 표준에 통합돼 JEDEC xSPI 호환 기술이기도 하다. 이런 특성에 기반해 하이퍼램을 사용하면 IC 공급사의 제품 설계 주기 또한 앞당길 수 있다.

윈본드는 하이퍼램 제품 라인에서 현재 32Mb, 64Mb and 128Mb 제품의 대량 생산을 시작했다. 24BGA(오토모티브 등급), 49BGA, WLCSP, KGD는 지금 바로 사용할 수 있다. 6×8mm² 크기의 24BGA와 달리, 4×4mm²의 크기를 갖는 49BGA는 컨슈머 웨어러블 시장을 겨냥한 제품이다. 윈본드는 20년 이상의 D램 제조 경험을 바탕으로 고객의 요구를 충족하는 우수한 제품을 계속 공급해 나갈 예정이다.

자료제공: 윈본드

그래도 삭제하시겠습니까?