알테라

서비스 공급업체들은 자본 비용 및 운영 비용의 증가, 매출 성장 감소 등에 직면함에 따라 100Gbit OTN 솔루션으로 전환하여 자신들의 기존 10Gbit 기반 네트워크들을 10배까지 확장하고 있다.

하지만 많은 구형 OTN, SONET, 이더넷, 스토리지 시스템들이 상대적으로 낮은 데이터 전송속도로 동작하고 있으며, 100Gbit OTN 먹스폰더(muxponder)를 사용하는 새로운 광 인프라스트럭처에 연결되어야만 한다. 알테라의 Stratix V FPGA 제품군은 100Gbit OTN 먹스폰더 솔루션의 요구사항을 직접적으로 해결할 수 있는 많은 주요 혁신 기술들을 포함하고 있다.

자료제공: 알테라(www.altera.com)

서론

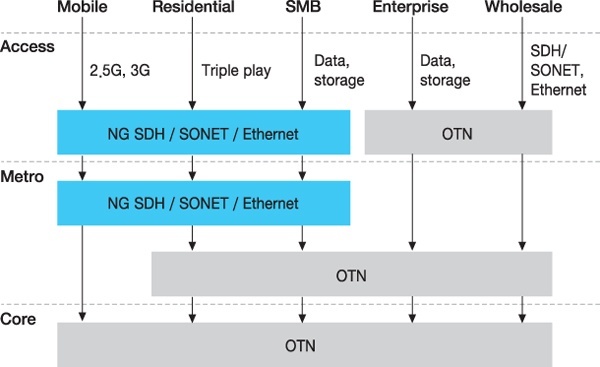

메트로 및 장거리 네트워킹 영역에서의 대역폭에 대한 폭발적인 수요로 인해 서비스 공급자들은 자신들의 WDM(wave length division multiplexing) 네트워크를 보다 효율적으로 활용할 수 있는 방법들을 찾고 있다. (그림 1)은 최신 OTN(Opti cal Transport Network) 인프라스트럭처로 구성된 서비스 및 대역폭 수요의 증가를 나타낸 것이다.

그림1. 최신 OTN 인프라스트럭처로 구성된 수요들

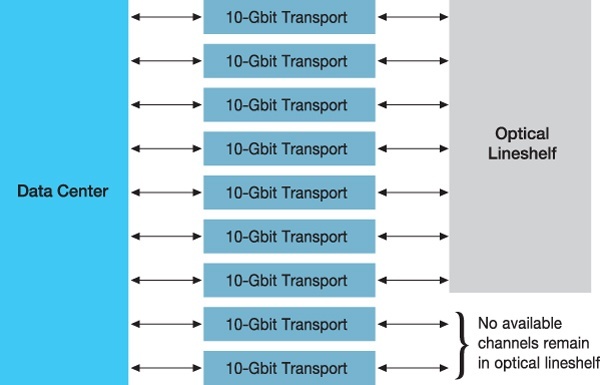

끝없이 증가하는 대역폭에 대한 이러한 수요는 P2P(peer-to-peer) 공유, 소셜 네트워킹, 디지털 비디오 전송, 광대역 무선 단말기, 화상회의, 비디오 메시지 등과 같은 끝없이 쏟아지고 있는 새로운 애플리케이션들에 의해 견인되고 있다. 과거에 서비스 공급업체들은 (그림 2)에 나타낸 바와 같이 자신들의 기존 WDM 네트워크에 단순히 보다 많은 채널들을 추가함으로써 이러한 성장을 유지하려 했다.

그림2. 전통적으로 서비스 제공업체들은 대역 요구가 증가함에 따라 보다 많은 채널들을 추가해왔다.

하지만 이러한 계획은 사용 가능한 채널들을 고갈시켜 서비스 공급업체들에게 자본 비용 및 운영 비용 증가, 매출 성장 감소 등의 문제에 직면하게 만들었다. 현실은 전통적인 10Gbit OTN 아키텍처는 그린필드 전개에서 대역폭 활용을 최적화시키는 비용-효율적인 구현방법을 활용할 수 없다.

40/100Gbit 이더넷의 도입과 채택, 그리고 OTN 표준의 수용을 통해 서비스 공급업체들은 현재 100Gbit OTN 솔루션으로 전환함으로써 자신들의 채널 성능을 10배까지 확장시키고 있다. 하지만 상대적으로 낮은 데이터 전송속도로 동작하는 많은 구형 OTN, SONET, 이더넷, 스토리지 시스템들이 있으며 새로운 OTN 인프라스트럭처와 어느 정도 연결되어야만 한다.

공간과 전력을 절감하면서 사용 가능한 대역폭을 극대화시키는 방법으로 이것을 달성할 수 있는 한 가지 방법은 상대적으로 낮은 데이터 전송속도를 지원하는 복수의 클라이언트 채널들을 상대적으로 높은 데이터 전송속도의 단일 파장에 통합시키는 것이다. 이것이 100Gbit OTN 먹스폰더(muxponder, multiplexing transponder)의 역할이다.

100Gbit OTN 먹스폰더 솔루션

전통적으로 OTN 시스템들은 1개 이상의 클라이언트 포트와 인터페이스하면서 이들을 광 전송 포트에 통합하는 라인 카드를 제공한다. 각 라인 카드는 특수한 클라이언트 프로토콜의 요구사항들, 그리고 특정 클라이언트 및 전송 데이터 속도를 충족시킬 수 있도록 설계되었다.

많은 다양한 클라이언트 형태가 존재하는 환경의 경우, 각 섀시에 많은 다양한 라인 카드들이 필요하다. 이것은 비용, 공간, 관리 측면에서 효율적인 솔루션이 되지 못하며 다양한 파장에서 전송되고 있는 개별 클리언트 페이로드가 되어 광섬유 케이블의 전체 효율을 저하시킨다.

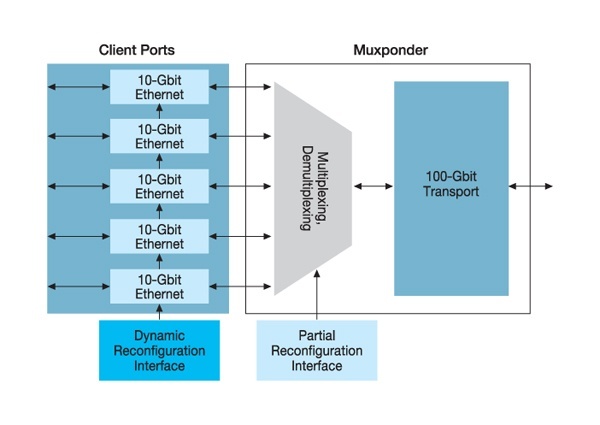

100Gbit OTN 시스템에 있어서 많은 다양한 프로토콜과 데이터 전송속도를 지원하는 단일 라인 카드를 이용하는 것이 보다 바람직하다. 동일 카드 상의 다른 클라이언트들의 동작에 영향을 미치지 않으면서 클라이언트의 변화하는 요구사항을 충족시키기 위해서 이 라인 카드는 서비스를 제공하면서 재구성될 수 있다. 또한 라인 카드는 상대적으로 낮은 속도를 가진 다수의 클라이언트 신호를 사용하여 단일 100Gbit 광 전송 신호로 통합 및 분리할 수 있다. 이 멀티플렉싱 및 디멀티플렉싱은 100Gbit OTN 먹스폰더의 주요한 기능이다(그림 3).

그림 3. 100Gbit OTN 먹스폰더 카드의 블록 다이어그램

현재 일부 DWDM(dense wavelength-division multiplex ing) ROADM(reconfigurable optical add-drop multiplex er) 시스템에 먹스폰더 카드가 사용되고 있지만 이들은 SAN (storage area networking), HD 비디오 전송 등과 같은 주요 서비스 성장 영역의 최신 요구사항들을 지원하지 않는 구형 멀티칩 솔루션에 기반하고 있다. 이러한 시장을 충족시키기 위해서 장비 제조업체들은 자신들의 플랫폼이 40/100Gbit 이더넷, 10Gbit 광 채널, HD-SDI, 3G-SDI 등과 같은 보다 높은 속도의 새로운 인터페이스들을 지원할 수 있도록 업데이트해야만 한다.

알테라의 Stratix V FPGA 제품군은 비용효율적인 차세대 100Gbit OTN 먹스폰더 솔루션을 구현하는 데 필요한 대역폭, 통합 수준, 그리고 혁신적인 기능들을 지원한다. Stratix V FPGA 기반의 먹스폰더 카드는 이더넷, SONET/SDH, SAN, HD-비디오 등과 같은 모든 서비스 형태를 효율적으로 지원할 수 있다. 이를 통해 장비 제조업체들은 기존 플랫폼들에 새로운 서비스를 추가할 수 있으며 보드 공간, 복잡성, 전력 등을 절감하면서 복수의 서비스별 카드를 통합할 수 있다. 추가적인 이점으로는 시스템-운영 및 관리 비용의 절감, 신뢰성 및 업타임의 증가 등을 들 수 있다.

Stratix V FPGA를 통한 100Gbit OTN 먹스폰더의 구현

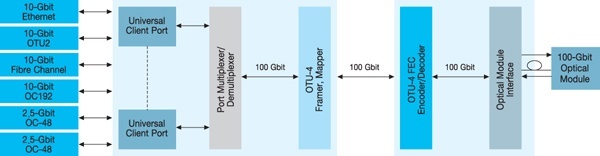

알테라의 28nm Stratix V FPGA는 단일 FPGA에서 제공될 수 있는 최고의 대역폭, 최고의 시스템 집적도, 최대의 유연성 등을 제공할 수 있는 많은 중요한 혁신 기술들을 통해 설계되었다. 다음과 같은 강화된 새로운 디바이스 기능들을 사용함으로써 Stratix V FPGA에 100Gbit OTN 먹스폰더를 구현할 수 있었다(그림 4).

그림4. Stratix V FPGA에 구현된 100Gbit OTN 먹스폰더의 다이어그램

·통합 시리얼 트랜시버는 600Mbps에서 12.5Gbps의 연속 범위와 20Gbps에서 28Gbps까지의 연속 범위를 지원하는 선택사항을 통해 라인측과 클라이언트측 인터페이스를 모두 지원한다.

·24bit 델타-시그마 변조 방법을 사용하는 통합 분주-합성 PLL은 클라이언트 레퍼런스 주파수를 생성하는 데 필요한 고가의 VCXO에 대한 요구를 제거한다.

·코어 로직의 부분적 재구성 기능을 통해 다른 클라이언트에 영향을 주지 않으면서 각 개별 클라이언트를 위한 프로토콜 로직을 추가, 제거, 변경할 수 있기 때문에 시스템 업타임을 극대화할 수 있다.

·트랜시버의 동적 재구성 기능을 통해 다른 트랜시버의 동작에 영향을 미치지 않으면서 모든 트랜시버에 대한 아날로그 PMA(physical medium attachment) 설정을 변경할 수 있다.

·재설계된 ALM(adaptive logic module)과 강화된 MultiTrack 라우팅 아키텍처를 제공하는 고성능 고밀도 저전력 FPGA 코어 로직은 사용자 로직 내의 넓은 병렬 버스를 지원하는 데 필요한 성능을 제공한다.

통합 시리얼 트랜시버

Stratix V FPGA는 최대 28Gbps의 데이터 전송속도로 동작하는 트랜시버를 최대 66개까지 제공한다. 각 트랜시버는 프로그래머블 프리-엠퍼시스, 이퀄라이제이션, 차동 출력 전압 등의 기능을 포함하고 있다. 최대 12.5Gbps의 데이터 전송속도에서 다양한 업계 표준과 전유 프로토콜에 대한 지원을 제공하는 포괄적인 PCS(physical coding sublayer)가 포함된다.

100Gbit OTN 먹스폰더 애플리케이션의 경우, 라인측 인터페이스는 공통 전송 PLL에 의해 구동되는 이들 트랜시버 10개를 그룹으로 사용한다. Stratix V FPGA는 라인측 프로토콜의 엄격한 지터 요구사항을 충족시키는 데 이상적인 로우-지터 IC(inductor-capacitor) 전송 PLL을 포함하고 있다. 라인측 데이터 전송속도는 요구되는 FEC(forward error correction) 기능에 따라 달라지며 일반적으로 9.9Gbps에서 12.5Gbps 사이의 범위에 있다.

향후에는 25Gbps에서 28Gbps까지 동작 가능한 4개의 트랜시버를 사용하여 구현될 것으로 예상되고 있으며 이러한 구성 역시 Stratix V FPGA에 의해 지원된다.

클라이언트측 인터페이스는 10개 이상의 트랜시버를 사용하며 그 각각은 자체 전송 PLL을 통해 독립적으로 클록킹된다. Stratix V 디바이스의 트랜시버 클록킹 아키텍처를 통해 채널의 독립적인 클록킹이 가능할 뿐만 아니라 라인측 인터페이스에 의해 요구되는 채널 본딩 역시 가능하다.

클라이언트측 데이터 전송속도는 다양한 클라이언트 프로토콜에 의해 결정되며 일반적으로 614Mbps에서 11.3Gbps 사이의 범위에 있다. 600Mbps에서 12.5Gbps까지와 20Gbps에서 28Gbps까지의 연속 동작 범위를 제공하기 때문에 Stratix V FPGA 내의 트랜시버는 이러한 애플리케이션에 이상적이다.

통합 분주-합성 PLL

100Gbit 먹스폰더 애플리케이션에서 단일 100Gbit 통합 데이터 스트림을 형성하기 위해 클라이언트 데이터 스트림이 함께 멀티플렉싱될 경우에 클라이언트 주파수에 대한 정보가 데이터 스트림에 추가되어 라인측 데이터와 함께 전송된다. 먹스폰더가 이 100Gbit 통합 데이터 스트림을 수신한 경우, 데이터 스트림에 포함된 개별 클라이언트 주파수 정보를 사용하여 필요한 클라이언트 주파수를 합성하고 원래의 클라이언트 데이터 스트림 각각을 분리시킨다.

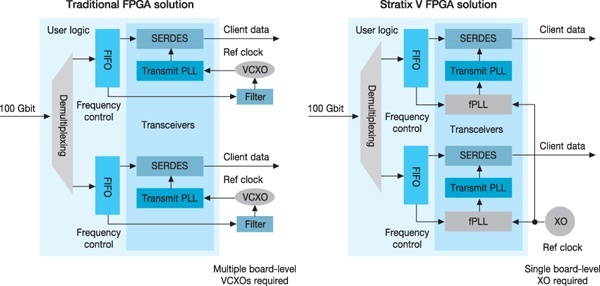

전통적으로 이 프로세스는 고비용의 보드-레벨 VCXO 뱅크를 필요로 한다. 하지만 Stratix V FPGA의 경우, 이들 VCXO가 통합 분주-합성 PLL에 의해 대체된다. 이를 통해 공간, 복잡성, 그리고 회로 보드에 대한 BOM(bill of material) 비용을 절감할 수 있다.

Stratix V FPGA는 24bit 3차 모듈레이터를 사용하는 분주-합성 PLL((fPLL)을 최대 32개까지 통합하고 있다. 이것은 약 1,600만분의 1의 해상도와 일치하는 것으로 주파수 합성이 보드-수준의 VCXO를 대체할 수 있을 만큼 정확해진다. (그림 5)는 Stratix V FPGA의 통합 fPPL을 통해 대체될 수 있는 보드 상의 VCXO 뱅크를 나타낸 것이다.

그림 5. Stratix V FPGA의 PLL을 사용하여 VCXO를 대체하는 방법

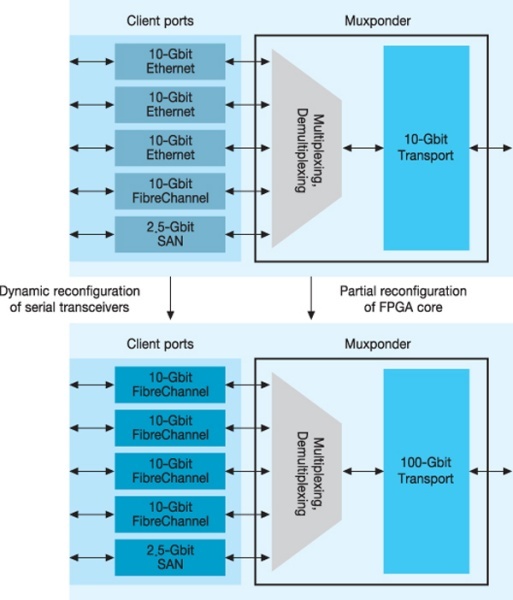

코어 로직의 부분적인 재구성과 트랜시버의 동적 재구성

일단 시스템 내에서 먹스폰더가 동작하면 필요에 따라 사용되는 클라이언트의 수를 증가 또는 감소시킬 수 있어야 하며 시스템의 나머지 부분은 계속해서 트래픽을 전달하고 정상적으로 동작해야 한다. 뿐만 아니라 일부 시나리오에서는 케이블이 프론트 패널 상에 재 정렬되는 경우에 1개 이상의 클라이언트 측 프로토콜이 변경되어야만 한다. 또한 시스템의 나머지 부분은 계속해서 트래픽을 전달하고 정상적으로 동작하면서 이러한 변경이 이루어져야만 한다.

이러한 시스템 변경들을 지원하기 위해서 Stratix V FPGA는 FPGA 코어의 부분적인 재구성과 시리얼 트랜시버의 동적인 재구성 기능 모두를 제공한다. 이러한 기법들(그림 6)은 비간섭적(non-intrusive)이기 때문에 FPGA의 나머지 부분들은 계속해서 정상적으로 동작하면서 변경이 이루어져서 시스템 업타임을 극대화시킨다.

그림 6. FPGA 코어의 부분적인 재구성과 트랜시버의 동적 재구성

클라이언트 인터페이스를 추가하기 위해서 트랜시버가 동적 재구성 기능을 통해 활성화 및 구성되고 프로토콜 로직과 멀티플렉싱 기능들이 코어의 부분적인 재구성을 통해 FPGA 코어에 추가된다. 사용되지 않는 클라이언트 인터페이스를 제거하기 위해서 트랜시버는 불활성화되고 클라이언트 로직이 FPGA로부터 제거되어 전체 전력소모를 절감한다.

고성능 저전력 FPGA 코어 패브릭

FPGA에서 100Gbit OTN 먹스폰더를 구현하기 위해서는 낮은 전력소모 특성과 함께 파이프라인 고효율 병렬 버스들을 지원할 수 있는 코어 패브릭이 필요하다. Stratix V FPGA는 이러한 요구사항들을 충족시킬 수 있는 다음과 같은 많은 주요 혁신 기술들을 포함하고 있다:

·강화된 ALM(adaptive logic module)은 사용 가능한 레지스터의 수를 2배로 증대시켜 많은 레지스터와 많은 파이프라인을 가진 설계에 대해서도 간편한 타이밍 클로저 방법을 제공한다.

·인접한 LE(logic element)에 보다 많은 연결을 제공하는 강화된 MultiTrack 라우팅 아키텍처는 시스템 성능을 증가시키고 로직 활용도를 향상시키고 조밀한 설계에 대해서도 컴파일링 시간을 줄여준다.

·고성능 소형 풋프린트를 제공하는 새로운 20Kbit 내부 메모리 블록은 빌트-인 ECC(error correcting code) 보호기능을 포함하고 있다.

·프로그래머블 전력 기술은 중요하지 않은 타이밍 경로들에 대한 코어의 정적 전력소모를 자동으로 감소시켜준다.

·클록 트리를 영역별로 온 및 오프 상태로 전환할 수 있기 때문에 동적 전력소모를 최소화하는 동시에 불필요한 스위칭 잡음을 차단할 수 있다.

·고성능 HKMG(high-K metal gate) 28nm 공정 기술은 0.85V 전력공급으로 첨단 성능과 전력효율 특성을 제공한다.

결론

메트로 및 장거리 네트워킹 영역에서의 대역폭에 대한 폭발적인 수요는 서비스 공급업체들이 자신들의 광섬유를 효율적으로 사용하도록 만들고 있다. 새롭게 부상하고 있는 한 가지 중요한 기법은 100Gbit OTN 먹스폰더를 사용하는 것이다. 알테라는 이러한 시장 요구를 인식하고 100Gbit OTN 먹스폰더 애플리케이션의 요구사항을 직접적으로 해결할 수 있는 많은 주요 혁신 기술들을 Stratix V FPGA에 통합했다.

완벽한 100Gbit OTN 먹스폰더 솔루션을 위해서 알테라는 또한 업계 선도적인 Quartus II 설계 소프트웨어, OTN 레퍼런스 설계, 협력업체 IP 솔루션, Stratix V 하드웨어 개발 키트 등을 제공하고 있다.

회원가입 후 이용바랍니다.

개의 댓글

댓글 정렬

BEST댓글

BEST 댓글

답글과 추천수를 합산하여 자동으로 노출됩니다.

댓글삭제

삭제한 댓글은 다시 복구할 수 없습니다.

그래도 삭제하시겠습니까?

그래도 삭제하시겠습니까?

댓글수정

댓글 수정은 작성 후 1분내에만 가능합니다.

내 댓글 모음