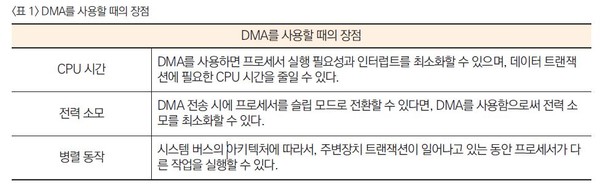

[전문 기술기고: 아나로그디바이스=브랜든 허스트(Brandon Hurst)]

임베디드 시스템에서 중요한 작업 중 하나가 외부 입력을 관리하는 것이다. 입력 관리가 프로세서에 불필요하게 연산처리 부담을 가중시킬 수 있으며, 이는 실행 시간을 늘리고 응답 시간을 늦추는 것으로 이어진다. 전력 소모를 최적화하고, 이벤트에 빠르게 응답하고, 대량의 연속적 데이터 전송을 관리하기 위해서는 DMA(direct memory access)를 채택한 마이크로컨트롤러를 사용하는 것이 최선의 방법일 수 있다.

▶ DMA(direct memory access)

주변장치들을 포함하는 시스템 애플리케이션은 마이크로프로세서가 병목 문제를 겪을 수 있는 지점들이 많다. 예를 들어 ADC가 데이터를 연속으로 전송하는 경우, 프로세서가 이를 관리하느라 자주 중단될 수 있는데 그러면 다른 작업을 완료하는 데 애를 먹게 된다. DMA는 데이터를 이동시키는 한 가지 방법으로서, 대량의 데이터나 또는 빠른 데이터 트랜잭션에 대한 프로세서의 관여를 최소화한다. DMA 컨트롤러는 메모리 및 주변장치와의 상호작용을 전담하는 코프로세서라고 생각하면 된다. 이는 한 쪽에서 데이터 트랜잭션이 이루어지는 동안, 다른 한 쪽에서는 메인 프로세서가 여러 주변장치들을 성공적으로 관리하거나, 다른 작업에 집중하거나, 또는 슬립 모드로 전환해서 전력 소모를 줄일 수 있게 해준다. 예컨대 Arm® 아키텍처 상에서, DMA 모듈은 LP2(슬립) 모드나 LP3(실행) 모드 동안 동작할 수 있다. 이는 웨어러블 센서 허브나 스마트 워치 같이 배터리 사용 시간을 연장하고자 하는 애플리케이션에서 특히 유용하다.

▶ 장점과 단점

DMA는 많은 디지털 시스템에서 유용하게 활용되며, 경우에 따라 DMA가 대량의 버스 트래픽을 관리해야 할 수도 있다. DMA는 네트워크 카드와 그래픽 카드에 사용되어 왔으며, 초기 IBM PC 일부 제품에 사용되기도 했다. 이는 다시 말해, 어떤 설계에 DMA를 적용하기 위해서는 약간의 절충점들이 있다는 뜻이기도 하다.

▶ 버스 액세스 및 CPU 사이클

DMA 컨트롤러는 전력 사용을 절약하거나 임베디드 시스템의 속도를 높인다는 점에서 매우 효과적이지만, 구현에 있어서 표준화가 많이 이루어지지 않았다. 일례로, 내부 버스 액세스 권한이 CPU와 동시에 부여되지 않도록 하기 위해 다양한 방식들이 사용되고 있다. 버스 액세스 방식의 가장 중요한 목표는 동일한 메모리 위치를 동시에 액세스하지 못하도록 하는 것이다.

만약 동시에 액세스가 이루어진다면 캐시 일관성 오류와 논리 오류가 발생할 것이다. 각각의 방식마다 서로 다른 하드웨어 또는 펌웨어 제어가 필요할 수 있기 때문에, 일반적으로 하나의 DMA 컨트롤러는 이러한 방식들 중 한 가지를 채택하도록 구성된다. 대부분의 DMA 컨트롤러에 주로 많이 사용되는 버스 액세스 방식으로는 버스트 DMA(burst DMA), 사이클 탈취 DMA(cycle-stealing DMA), 투명 DMA(transparent DMA)를 들 수 있다.

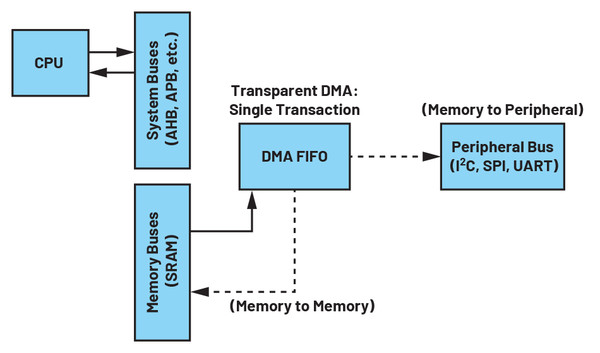

투명 DMA는 한 번에 한 가지 동작만을 실행할 수 있지만, 프로세서가 원하는 데이터 또는 어드레스 버스에 엑세스를 제공하는 명령을 실행하기를 반드시 기다려야한다. 이 액세스 제한을 검증하기 위해서 추가적인 로직이 필요하다. 대체로 이 타입의 DMA가 가장 속도가 느리다. 투명 DMA는 메모리 버스에 액세스할 필요 없이 추가적인 프로세싱을 하는 애플리케이션에 유용하다. 이 방식의 장점은 CPU가 작업을 완전히 멈출 필요가 없기 때문에 CPU 스로틀링(throttling)을 없앨 수 있다는 것이다.

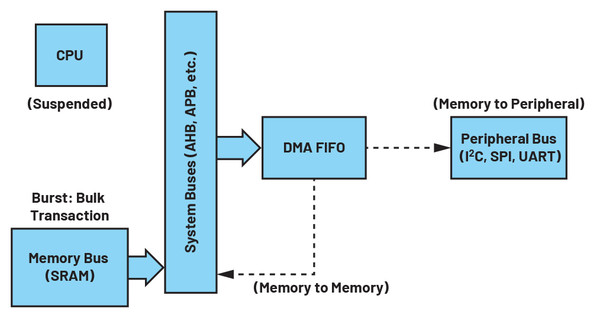

버스트 DMA는 용량이 큰 버스트를 띄엄띄엄 전송하는데, 해당 DMA 컨트롤러가 목표한 버퍼로 그 버퍼가 수용할 수 있을 만큼 많은 데이터를 전송한다. 이 DMA 컨트롤러는 아주 짧은 간격 동안 CPU 동작을 차단하고, 큰 용량의 메모리를 옮긴 다음에 버스를 다시 메인 CPU에게 돌려주는데, 전송을 완료할 때까지 이 과정을 되풀이한다. 버스트 DMA는 일반적으로 가장 빠른 DMA 타입으로 알려져 있다.

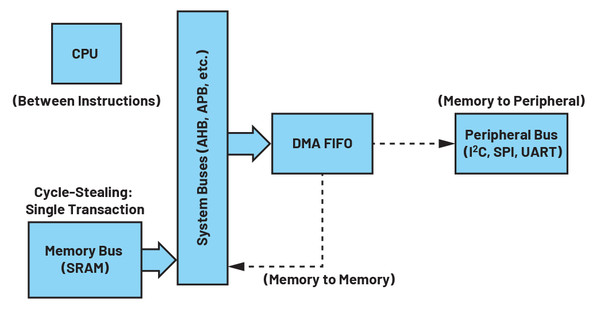

이와 달리 단일 바이트 전송 혹은 사이클 탈취 DMA는 CPU로부터 지시를 받아서 CPU 명령들 사이에 동작을 수행한다. 이는 2개 CPU 사이클 사이에 단일 동작을 삽입하므로, 사실상 CPU 시간을 ‘탈취’하는 셈이다. 한 번에 한 가지 동작만 실행하는 한계 때문에, 대체로 버스트 DMA보다 느리다.

▶ 버스트 DMA 아키텍처의 예시

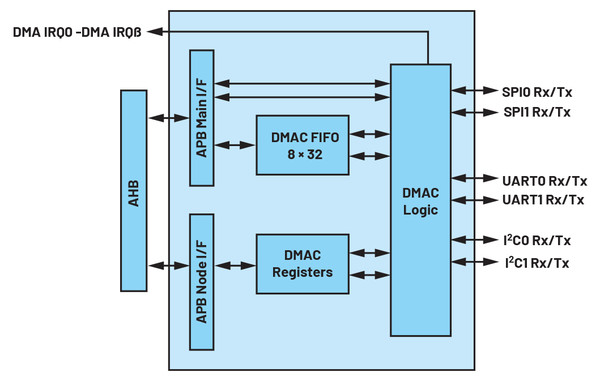

버스트 DMA 컨트롤러를 채택하고 있는 디바이스의 예로서 MAX32660을 들 수 있다(그림 4). AHB(advanced high performance bus)와 DMA 로직 사이의 위쪽 경로는 데이터 플로우를 나타내고, 아래쪽 경로는 제어/상태 플로우를 나타낸다. 구성에 따라서 DMA 컨트롤러가 AHB와 메모리 또는 주변장치 모듈 사이의 버퍼 인터페이스로서 동작할 수 있다. DMA 로직이 DMA 버퍼와 각 주변장치 사이에 자리잡고 트랜잭션 동안에 각 주변장치 버스를 개별적으로 관리한다. DMA 동작으로 한 번에 최대 32바이트를 옮길 수 있다. 다만, 소스/목표 버퍼가 그만한 데이터를 저장할 수 있어야 한다. 이 버퍼는 최대 16MB를 유지할 수 있으며, 내부 메모리 전송 외에도 송신 또는 수신 I2C, SPI, I2S, UART로 구성할 수 있다. DMA 제어를 프로그래밍하는 것은 프로토콜마다 약간씩 다를 수 있으나, 주변장치 트랜잭션은 전적으로 DMA 컨트롤러가 관리한다. 중재 모듈이 4개 DMA 채널과 CPU 사이에 버스 액세스 제한을 제어하고 우선순위 체계에 따라서 요청을 승낙한다.

▶ DMA 옵션을 제공하는 최신 마이크로컨트롤러 제품들

DMA는 여러 센서들을 관리하고 높은 쓰루풋, 효율, 저전력 동작을 요구하는 최신 임베디드 시스템에서 중요한 기능이다. DMA 컨트롤러는 메모리 및 주변장치 버스 트랜잭션을 전담하는 코프로세서로 볼 수 있다.

전력 소모를 최소화하고 프로세서의 부담을 덜고자 하는 애플리케이션에서는 DMA를 사용할 필요가 있다. 예를 들어 의료용 웨어러블 기기는 대량의 데이터를 처리하면서 배터리 전하를 되도록 절약해야 하며, 그러면서 또한 민감한 데이터를 취급해야 한다. 저전력 웨어러블 기기 설계에 적합한 마이크로컨트롤러로서 아나로그디바이스(Analog Devices)의 MAX32660과 MAX32670은 속도가 빠른 버스트 DMA 아키텍처를 채택하고 있다. DARWIN Arm 마이크로컨트롤러서 MAX32666은 블루투스 5를 통합하고 있어 웨어러블 및 IoT 애플리케이션에 사용하기에 적합하다. 이들 디바이스 제품은 2개의 8채널 버스트 DMA 컨트롤러를 포함하며, 이벤트 기반 트랜잭션을 지원한다. 또한 이들 제품은 보안 부트로더와 ECDSA, SHA-2, AES 암호화를 가속하기 위한 TPU(trust protection unit)를 비롯해서 동급 최상의 보안 하드웨어를 특징으로 한다. 초기의 IBM PC부터 네트워크 카드, 나아가 이제는 보안이 강화된 저전력 웨어러블과 IoT 기기 같은 최신 디지털 시스템에서 DMA가 필수적인 역할을 한다.

그래도 삭제하시겠습니까?