분할 생산 ‘수율개선’ 가능…글로벌 빅테크 전용칩 개발 활발

[테크월드뉴스=노태민 기자] 반도체 미세공정 경쟁이 끝에 다다랐다는 주장이 제기되고 있다. 3나노미터(nm) 미만 경쟁은 기술 한계와 비용 상승 등의 이유로 지속되지 못한다는 이유다. 향후 반도체 업계 경쟁은 미세공정이 아닌 후공정, 칩렛 등에서 이뤄진다는 전망이다.

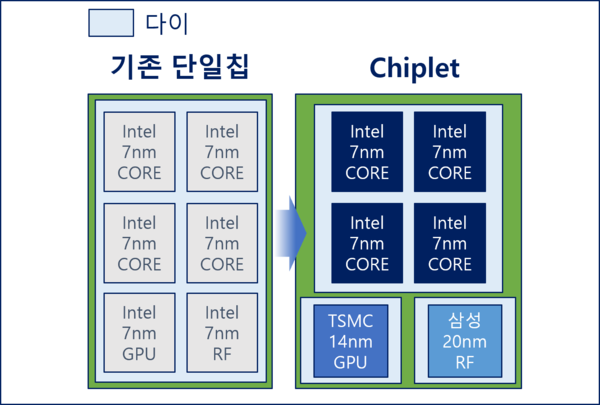

칩렛(반도체 조각)은 프로세서를 구성하는 작은 구성 단위 혹은 IP(Intellectual property) 블록 단위로, 각기 다른 기능을 수행하는 여러 칩렛을 연결해 프로세를 만드는 기술이다. 기존 단일(Monolithic) 칩의 성능 한계 및 높은 비용을 극복하기 위해 등장했다. 가장 큰 특징은 제조사와 선폭이 상이한 이종칩의 결합이 가능하다는 점이다.

다만 칩렛 기술을 이종칩을 결합하는 기술로 상대적으로 칩 전체 크기가 커질 수밖에 없다. 칩 크기 제약으로 공간 제약이 적고 고부가 영역인 서버, HPC, 오토모티브 등에 우선 적용되고 있다.

![단일칩 대비 칩렛 다이 크기별 수율. [자료=유니마이크론]](https://cdn.epnc.co.kr/news/photo/202210/228562_229651_2259.png)

업계에서 칩렛을 주목하는 이유는 동일한 성능을 가진 반도체를 보다 낮은 비용으로 생산할 수 있는 이유다. 반도체는 다이가 커질수록 수율이 하락한다. 작은 다이에 분할 생산하면 수율 향상이 가능하고 생산 가격하락으로 이어진다.

선폭이 상이한 이종칩 결합이 가능한 점도 칩렛 기술의 장점이다. 고성능 칩이 필 필요한 부분과 저성능 칩이 적용되는 부분에 적합한 칩 적용이 가능하다.

목적별로 유연한 칩 선택이 가능해 제작 및 설계 비용 감소가 가능하다. 설계‧제작의 진입장벽도 낮아져 전용 칩 생산을 원하는 빅테크 기업의 진출이 가능하다.

현재 마이크로소프트, 알리바바클라우드, 구글 클라우드, 메타 등의 빅테크 기업은 칩렛 기술을 통한 자사 칩 개발에 나서고 있다.

2022년 하반기 출시가 예상되는 인텔의 서버용 CPU ‘사파이어 래피즈’는 칩렛 기술이 적용된 대표제품이다. ‘사파이어 래피즈’는 칩렛 기술을 적용해 AI 등의 분야에서 전작 대비 2배 이상 향상된 성능이 기대된다.

반도체 업계에서는 칩렛 기술 활성화를 위해 최근 UCIe(Universal Chiplet Interconnect Express)를 발족했다. UCIe는 제조사와 선폭이 상이한 칩의 호환성 문제를 방지하기 위해 만들어진 80여 개 반도체 기업의 연합체다. 주요 참여 기업으로는 회장사인 인텔, 삼성전자, TSMC, 메타, 마이크로소프트 등이 있다.

반도체 업계 관계자는 “칩렛 기술 활성화를 위해 파운드리, 팹리스, OSAT, 디자인 하우스 등의 기업들이 전례 없는 컨소시움을 결성했다”며 “칩렛 기술은 서버, HPC, 오토모티브 등의 분야에서 빠르게 활성화될 것”이라고 전망했다.

그래도 삭제하시겠습니까?