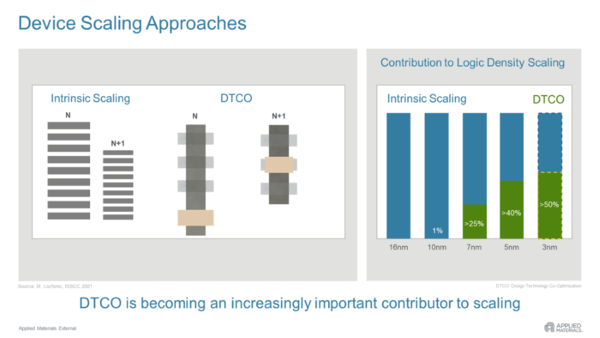

[어플라이드머티어리얼즈=우데이 미트라(Uday Mitra)] 3나노미터(nm) 노드 로직 밀도 개선의 절반은 전통적인 2D 공정 미세화, 나머지 절반은 설계 기술 공동최적화(DTCO, Design Technology Co-Optimization)에 힘입은 바가 크다.

기존 공정 미세화가 50년 이상 충실한 역할을 해온 가온데, 최근에는 DTCO가 무어의 법칙이 둔화되는 것을 보완하고 있다. DTCO는 로직 셀의 미세화, 밀도 증진, 면적당 비용 개선의 새로운 방법을 제시한다.

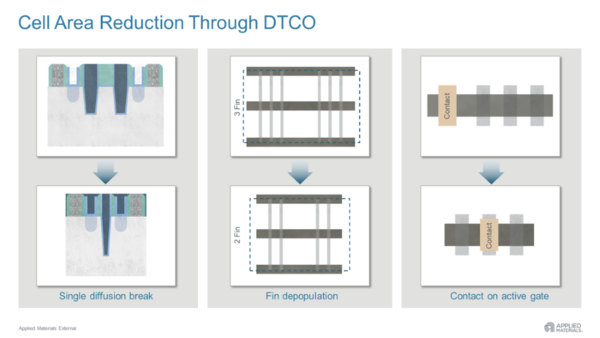

DTCO는 로직 셀 요소의 레이아웃을 스마트하게 변화시켜 리소그래피 회로 선폭 개선과 트랜지스터의 독립적인 추가 미세화를 가능케 한다. 예를 들어 개별 로직 셀을 절연하는 과정에서 설계자들은 인접한 장치를 분리하기 위한 더블 디퓨전 브레이크(DDB, Double Diffusion Break)를 싱글 디퓨전 브레이크(SDB, Single Diffusion Break)로 대체함으로써 확실한 미세화 을 제공한다. 설계자들은 트랜지스터 당 핀 수도 3개에서 2개로 줄이고, 트랜지스터의 전기 전극을 측면에서 상단으로 이동시켜 게이트 상단의 전극 구현을 추구해왔다.

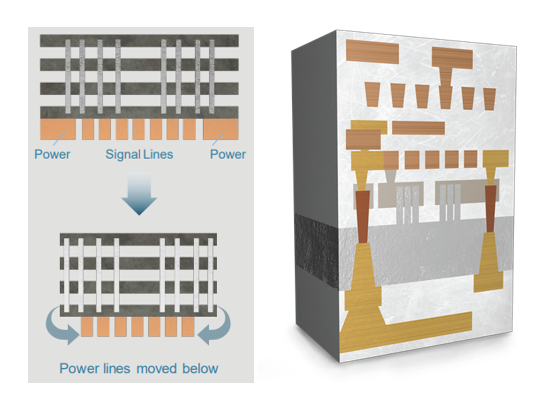

후면 배전망

트랜지스터와 로직 셀은 웨이퍼 하부에 위치한다. 오늘날 전력과 신호는 모두 상부에서 라우팅 돼 칩의 각 금속 레이어를 통해 하달된다. 두께가 더 두꺼운 전력 라인은 스위칭에 필요한 전력을 제공하는 반면, 얇은 신호 라인은 스위칭 시기를 결정한다. 각 금속 레이어에는 전기 저항이 있으며, 공급 전압의 일부는 손실돼 전력을 낭비하고 열을 발생시킨다.

후면 배전망은 두꺼운 전력 라인이 웨이퍼 후면을 통한 재배열로 웨이퍼 아래 트랜지스터로 연결된다. 업계는 이 같은 DTCO 배선 혁신을 통해 최대 25%까지 전력 소비량을 개선할 수 있을 것으로 기대한다. 또한 접근 방식에 따라 로직 밀도를 6~30%까지 높일 수 있다.

GAA 트랜지스터

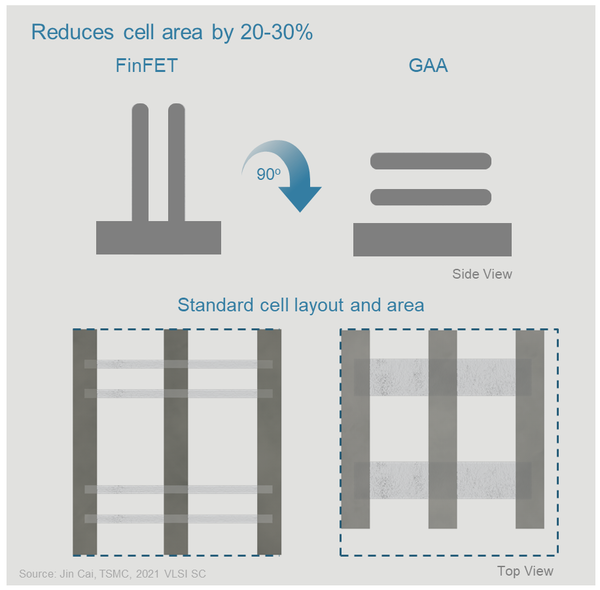

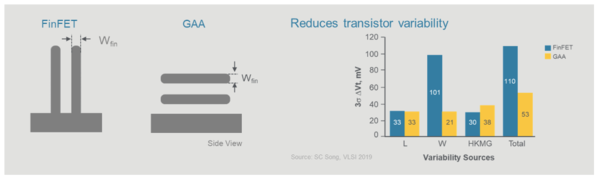

게이트올어라운드(GAA, Gate-All-Around) 트랜지스터는 2010년 평면 2D 트랜지스터에서 3D 트랜지스터로의 변화를 가져온 핀펫(FinFET) 이후 반도체 설계 분야에서 일어난 가장 큰 변곡점 가운데 하나다.

GAA를 DTCO 형태로 설명하는 것은 직관적이지 않을 수 있다. 하지만 GAA는 트랜지스터의 요소를 동등한 리소그래피 선폭에서 핀펫 대비 로직 밀도를 높이는 방식으로 효율적으로 재배열하므로 DTCO 형태로 설명하는 것은 타당하다.

개념상 GAA는 핀펫 트랜지스터를 90도 회전시킨 것과 유사하다. 이 게이트가 4면의 실리콘 채널을 감싸 3면만 감싸는 핀펫보다 개선됐다. DTCO의 이점은 로직 셀이 X와 Y 축 모두에서 축소된다는 데 있다. 또한 나노시트의 폭을 넓혀 구동 전류를 높임으로써 성능은 최대 25%, 밀도는 25% 가량 높일 수 있다.

에피택시∙선택적 제거는 GAA 전력 및 성능의 관건

제조사 관점에서 보면 GAA는 핀펫 제작에 사용되는 많은 검증된 공정을 차용하고 있다. 그러나 주요 차이점은 실리콘 채널의 폭과 균일성을 결정하고 통제하는 방식이다. 핀펫에서 채널 폭은 리소그래피와 식각에 의해 결정되며, 트랜지스터 성능을 저하시키는 편차가 발생하는 경향이 있다. GAA에서 채널 폭은 정밀도가 더 높은 에피택시와 선택적 제거에 의해 결정되며, 채널 균일성과 트랜지스터 성능을 높여준다.

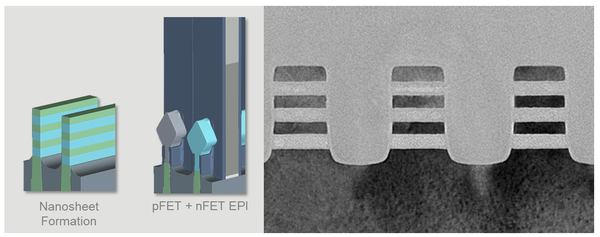

GAA는 두 가지 에피택시를 채택했다. 빠른 속도의 평판 에피택시는 실리콘의 대체 레이어와 실리콘 저마늄을 증착해 나노시트를 형성하는 데 사용된다. 속도가 느린 선택적 에피택시는 이후 나노시트에 변형 공학을 적용하는 데 사용되며 트랜지스터 성능을 최적화한다. 결국 선택적 물질 제거는 희생시트인 실리콘 저마늄 레이어를 제거하기 위해 사용되며, 이 실리콘 저마늄 레이어는 트랜지스터가 동작 상태일 때 전자가 흐르는 실리콘 채널 형성을 지원하는 데에만 사용된다.

이 채널들은 트랜지스터를 완성하기 위해 추가적인 엔지니어링이 필요하다. 게이트 산화물은 채널의 모든 면을 감싸도록 증착돼야 한다. 게이트 산화물이 얇을수록 구동 전류가 높아져 스위칭 성능을 최적화하고 누설 전류가 낮아져 전력 소비량과 발열량을 줄인다. 게이트 산화물 미세화는 수 년 간 정체돼 왔는데 이 같은 혁신은 반도체 제조사에게 좋은 소식이다.

게이트 산화물 및 고유전율 메탈 게이트를 미세화하는 새로운 방법

게이트 산화물은 트랜지스터의 온오프 상태를 제어하는 고유전율 메탈 게이트(HKMG, High-K Metal Gate) 스택에 의해 감싸져야 한다. GAA 채널 사이 공간이 핀펫에 비해 훨씬 협소한 10나노에 불과하기 때문에 이 게이트를 엔지니어링하는 일은 매우 어렵다. 배터리를 장착한 모바일 기기부터 고성능 서버에 이르기까지 특정 엔드 마켓에 사용되는 반도체 칩의 전력과 성능을 최적화하기 위해 이 메탈 게이트 스택의 폭은 엔지니어링이 요구된다. 극히 작은 공간에서도 임계치(threshold) 튜닝을 가능케 하는 솔루션이 필요하다.

앞서 언급한 것처럼 DTCO를 통해 리소그래피 선폭과 독립적으로 로직 밀도를 높일 수 있으며, 후면 배전망, GAA 트랜지스터, 포크시트, CFET(Complementary FET) 등의 미래형 트랜지스터 컨셉도 이와 같은 역할을 한다. 이제 EUV가 존재하므로 패터닝의 한계는 없다. 대신 우리는 나날이 작아지는 트랜지스터 전극 및 배선에 수반되는 기하급수적 저항 증가로 어려움을 겪고 있다.

그래도 삭제하시겠습니까?