삼성전기, 네패스 등 국내 기업도 관련 기술 개발-투자 집중

반도체 업계가 직접도를 향상시키기 위한 방법으로 차세대 패키징 기술인 FOWLP(Fan-Out Wafer Level Package) 기술에 주목하고 있다.

다수의 증권사 분석 자료에 따르면 오는 9월에 출시 예정인 애플 아이폰7의 AP은 처음으로 파트너사인 TSMC의 FOWLP 기술이 적용될 것으로 예상되고 있다.

삼성전기의 경우 2632억원을 관련 기술 시장에 투자하면서 FOWLP 생산라인을 삼성디스플레이 천안공장을 임대해 신축하기로 지난 7월 결정했다. 업계는 삼성전자의 갤럭시 시리즈의 AP에도 삼성전기의 FOWLP 기술 적용 여부에 대해 주목하고 있다.

키움증권 분석 자료에 따르면 삼성전기는 2632억원 중 1000억원은 유틸리티, 클린룸 등 인프라 구축에 쓰이고 1600억원은 1개의 개발라인을 위한 투자할 계획이다. 회사 측은 전력관리 IC인 PMIC 등을 시작으로 2018년부터 매출 발생을 예상하고 있다.

반면 애플에 탑재되는 A10 프로세서를 위한 TSMC의 패키지는 6만8000㎡ 클린룸에서 양산되고, 생산능력은 월 3000만개, 웨이퍼 기준 월 8만장 이상으로 파악된다.

국내 OSAT 기업인 네패스의 경우 이미 FOWLP 기술 상용화에 성공했으며 오토모티브 시장을 중심으로 NXP반도체에 기술을 접목해 공급하고 있다. 앰코테크놀로지는 일본 패키지 업체 J-디바이스 인수 후 인천 송도에 건설 중인 신규 패키지 공장 `K5`에서 FoWLP 양산에 나설 계획이다.

최근 반도체 패키징 기술에 대한 관심이 뜨거운 이유는 반도체의 수요처가 기존의 스마트폰을 넘어 의료용, 웨어러블기기, 자동차, 산업용 등으로 다양해졌기 때문인 것으로 보인다. 패키지의 역할은 IC의 보호 및 연결 기능을 넘어 시스템 집적화(System Integration)로 변화되고 있는 추세다.

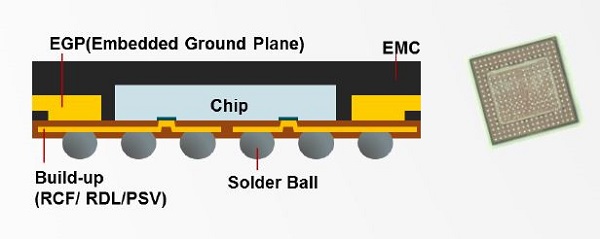

FOWLP 기술은 반도체 칩을 연결하기 위한 볼을 밖으로 빼 내는 팬아웃(Fan-Out) 형식의 범핑 공정으로 인해 두께가 얇아지고 비용절감 효과가 있으며 전기적 성능과 에너지 소모를 최소화하는 장점이 있다.

특히 반도체 미세 공정화 기술이 도입되면서 28나노 이후로는 고가 설비 등으로 지제 원가가 상승하고 있는 현실이다.

20나노 공정부터는 물리적으로 회로 선폭을 줄이는데 어려움이 따르는데다 설계, 공정, 장비, 재교 비용도 큰 폭으로 늘어나기 때문에 28나노 공정보다 칩 면적이 축소돼도 오히려 원가는 상승하기 때문이다. 반도체 미세 공정화에 따른 원가 감소의 한계로 인해 후공정 패키지 기술이 주목받고 있는 이유다.

FOWLP 기술은 입출력(I/O) 밀도를 높일 수 있고 3D 등 집적화에 유리한 것도 이점이다. 예컨대 반도체의 고성능화로 인해 스마트폰에 탑재된 AP의 I/O 단자수가 증가함으로써 제조업체들은 FOWLP 기술을 적용하는 방안을 선택하고 있다.

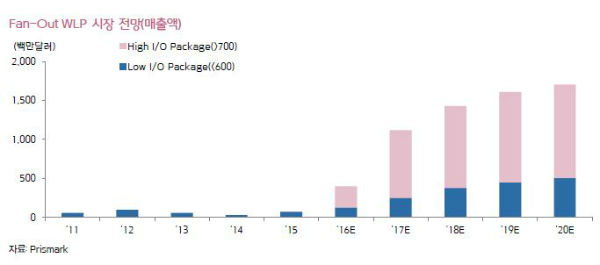

FOWLP 기술 투자는 향후 더욱 확대될 것으로 보여 진다. PCB 시장조사기관 프리마크(Primark)에 따르면 FOWLP 시장 규모는 애플의 고성능 AP가 채택한 것을 계기로 향후 수년간 모바일 칩 중심으로 올해 4억달러에서 2020년 17억달러에 이르며 연평균 89% 성장하고, 수량 기준으로는 올해 4.4억개에서 2020년 20억개로 연평균 69% 성장할 것으로 전망했다.

그래도 삭제하시겠습니까?