글= 헤이송 덩(Haisong Deng) 아나로그디바이스 선임 애플리케이션 엔지니어

[테크월드뉴스=이광재 기자] 이 글은 다양한 첨단 기술 애플리케이션에서 첨단 전원 솔루션의 필요성에 대해 살펴본다.

이러한 애플리케이션은 DDR, 코어, I/O 디바이스와 같은 구성 요소를 위한 다수의 저전압 전원을 필요로 하며 반도체 집적도의 증가로 인해 마이크로프로세서의 전력 소비도 점점 더 커지고 있다.

이러한 요구를 충족시키기 위해 전압, 전류, 온도 등의 파라미터를 모니터링할 수 있는 텔레메트리 기능의 필요성이 커지고 있는 가운데 이 글에서는 디지털 전력 시스템 관리 기능이 통합된 2상 스텝다운 레귤레이터 설계를 소개한다. 이 설계는 크기, 효율, 루프 안정성, 과도 응답과 같은 핵심 목표를 달성하는 데 중점을 두고 있다.

서론

오늘날의 산업, 자동차, 서버, 통신 및 데이터 통신 애플리케이션들은 첨단 SoC, FPGA, 마이크로프로세서 솔루션을 요구한다. 이러한 솔루션은 DDR용으로 1.1V 전원, 코어용으로 0.8V, I/O 디바이스용으로 3.3V 또는 1.8V 등 여러 개의 저전압 전원을 필요로 한다.

반도체 집적도의 증가로 인해 마이크로프로세서는 더 많은 전력을 소비하게 됐고 이에 따라 더 높은 공급 전류가 필요해졌다. 또 FPGA나 마이크로프로세서를 사용해 디바이스의 전압, 전류, 온도 및 기타 파라미터를 모니터링할 수 있는 텔레메트리 기능에 대한 수요도 높아지고 있다. 이러한 설계를 단순화하기 위해 I2C/PMBus가 통합된 아날로그 전력 IC를 사용하면 주요 파라미터를 모니터링하고 텔레메트리를 제어할 수 있다.

결과적으로 전원 솔루션은 텔레메트리 판독 및 레귤레이터의 프로그래밍이 가능하도록 I2C/PMBus 통신 기능을 통합해야 함은 물론 이와 동시에 더 높은 전류 처리 능력, 우수한 효율, 뛰어난 전자기 간섭(EMI) 성능을 제공해야 한다. 이러한 요구를 만족시키는 고성능 다상(multiphase) 부품들이 점점 더 보편화되고 있다.

이 글에서는 2상 스텝다운 레귤레이터 설계를 소개한다. 이 설계는 두 채널에서 최대 40A의 연속 전류를 공급할 수 있으며 각 채널당 최대 30A 부하를 지원한다. 또 PMBus/I2C 호환 직렬 인터페이스를 통해 프로그래밍과 텔레메트리가 가능한 디지털 전원 시스템 관리 기능도 통합하고 있다. 크기, 효율, 루프 안정성 및 과도 응답과 같은 설계 목표를 달성하기 위해서는 시스템에 필요한 부품을 신중하게 고려해서 선택할 필요가 있다.

효율이 중요한 이유

저전압 고전류의 전원 공급이 필요한 애플리케이션, 예를 들어 12V 전원으로부터 1V, 30A가 필요한 애플리케이션의 경우 효율이 80%라면 총 손실은 7.5W에 이른다. 이러한 손실은 IC와 인덕터에서 열에너지로 변환돼 온도를 상승시킨다.

데이터센터의 주변 온도는 일반적인 실내 온도보다 높은 경우가 많기 때문에 추가적인 손실은 IC 온도를 더욱 상승시키며 이는 IC의 열 차단 한계(일반적으로 150°C)에 가까워지는 결과를 초래할 수 있다.

이러한 문제는 DC-DC 컨버터가 고발열 마이크로프로세서 근처에 위치하는 경우가 많은 POL(point-of-load, POL) 애플리케이션에서 더욱 중요하게 작용한다.

다음 섹션에서는 저전압 고전류 DC-DC 컨버터 설계에서 효율을 향상시키는 여러 방법들을 소개한다.

스위칭(SW) 노드에서 PCB 트레이스

이전 버전의 2상 부품 데모 보드 설계에서는 <그림1>과 같이 위상 1과 위상 2의 인덕터가 서로 마주보도록 배치돼 있다. 이러한 방식으로 인덕터를 배치하면 EMI 성능이 더 우수해진다.

하지만 이 배치의 단점은 스위칭(SW) 노드의 트레이스가 비교적 길어지고 이로 인해 PCB 트레이스 손실이 증가할 수 있다는 점이다. 특히 중부하 조건에서는 이러한 손실이 더 커지는데, 이는 도통 손실이 전류의 제곱에 비례하기 때문이다(P=I²R).

![[그림1] Rev1 보드 레이아웃: CH1과 CH2 인덕터가 서로 마주보도록 배치. EMI 성능은 우수하지만 손실이 증가함 [제공=ADI]](https://cdn.epnc.co.kr/news/photo/202508/321281_326343_406.jpg)

<그림2>는 20A 부하 조건에서의 열화상 이미지를 보여준다. 스위칭 노드가 매우 뜨거워져 IC와 거의 동일한 수준의 온도 상승을 나타낸다. PCB 트레이스에 의한 손실은 적절한 설계를 통해 개선할 수 있다.

![[그림2] 실온 환경의 12 VIN, 0.6 VOUT, 20A 부하 조건에서 촬영한 열화상 이미지 [제공=ADI]](https://cdn.epnc.co.kr/news/photo/202508/321281_326344_4027.jpg)

<그림3>의 테스트 설정에서는 PCB를 절단하고 CH1 인덕터를 IC에 더 가깝게 이동시켜 스위칭 노드 트레이스를 줄였다.

![[그림3] 인덕터를 IC에 더 가깝게 배치 [제공=ADI]](https://cdn.epnc.co.kr/news/photo/202508/321281_326345_4051.jpg)

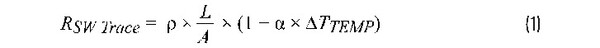

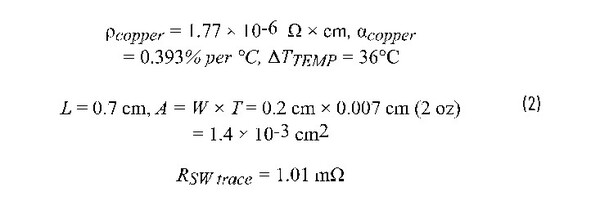

구리 두께와 PCB 트레이스 길이에 따라 SW 노드는 다음과 같은 직류 저항(DC 저항)을 갖는다.

여기서

총 손실은 다음과 같다.

여기서

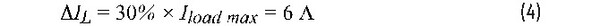

20A 부하 조건에서 SW 노드에서 발생하는 예상 손실은 다음과 같다.

SW 트레이스 길이 L = 0.3cm로 줄인 후 개선된 손실은 다음과 같다.

예상되는 손실 개선 효과를 계산한 결과는 다음과 같다.

<그림4>는 테스트 결과를 기반으로 한 효율 개선을 보여준다. 손실 개선 효과는 20A 부하 조건에서 0.22W, 30A 조건에서는 0.53W다.

![[그림4] 12VIN, 0.6VOUT, 1MHz, CH1 FCM VBIAS=5V에서의 효율 향상 [제공=ADI]](https://cdn.epnc.co.kr/news/photo/202508/321281_326353_4219.jpg)

부하가 커질수록 효율 차이는 더 커지는데 이는 PCB 트레이스에서의 도통 손실(P=I²R)이 지배적으로 작용하기 때문이다. 최대 부하 조건에서는 효율이 최대 1.5%까지 향상될 수 있다.

인덕터를 IC에 이렇게 가깝게 이동시킬 수는 없기 때문에 Rev2 보드에서는 <그림5>와 같이 인덕터를 90° 회전시켜 IC를 향하도록 배치해 SW 트레이스 길이를 줄였다.

![[그림] Rev2 보드 레이아웃: CH1과 CH2 인덕터가 IC를 향하도록 배치. 효율은 향상되지만 상대적으로 EMI는 악화됨 [제공=ADI]](https://cdn.epnc.co.kr/news/photo/202508/321281_326354_4244.jpg)

더 많은 CIN으로 VIN 링잉 억제

연구 결과 입력 커패시터(CIN)는 저전압 고전류 애플리케이션의 효율과 안정성에 큰 영향을 미친다. 그러나 많은 엔지니어들이 입력 커패시터 설계의 중요성을 간과하고 과거 경험에 따라 커패시터를 배치하는 경우가 많다.

또 전체 PCB 솔루션 크기의 제약으로 인해 입력 커패시터 수를 줄이는 경우가 있는데 이는 시스템의 불안정성과 더 많은 손실로 이어질 수 있다.

![[그림6] 입력 커패시터 블록 다이어그램 [제공=ADI]](https://cdn.epnc.co.kr/news/photo/202508/321281_326355_4347.jpg)

<그림6>은 왼쪽에서 오른쪽 순으로 핫 플러그 및 서지 전류 억제를 위한 전해 커패시터, 입력 전류 리플을 줄이기 위한 대형 세라믹 커패시터(보통 1210 또는 1206 사이즈), 고주파 리플을 억제하기 위한 소형 세라믹 커패시터(0402 또는 0201 사이즈)를 보여준다.

이 외에도 사일런트 스위치(Silent Switcher 2) 기술의 경우 고주파 스위칭 노이즈 및 오버슈트를 더욱 줄이기 위해 한 쌍의 커패시터가 패키지에 내장된다.

<그림6>의 오른쪽 사진은 디캡슐레이션 기법을 통해 내부 구조를 드러낸 것으로 1206 세라믹 커패시터 2개(노란색), 패키지 외부에 0402 커패시터 4개(파란색), 패키지 내부에 0402 커패시터 4개(빨간색)가 확인된다. 다이 위로 패키지에 구멍을 뚫어 기판 위에 위치한 패키지 내부 커패시터가 노출되도록 했다.

이러한 입력 커패시터들을 스위칭 노드와 함께 프로빙함으로써 서로 다른 입력 커패시터 조합에 따른 동작 특성을 관찰할 수 있다.

![[표1] 입력 커패시터(CIN) 조합 [제공=ADI]](https://cdn.epnc.co.kr/news/photo/202508/321281_326356_4845.jpg)

하지만 큰 CIN 조합을 사용하면 IC의 최대 동작 온도 범위가 150°C(X8L)에서 125°C(X7R)로 낮아지는 트레이드오프가 생긴다. 경우에 따라 IC의 최대 동작 온도가 중요한 고려 요소가 될 수 있다.

예를 들어 데이터센터와 같은 많은 애플리케이션의 주변 온도는 70°C를 초과하기 때문에 X7R 패키지 내부 커패시터를 사용할 경우 최대 온도를 초과할 가능성이 있다. 엔지니어는 이러한 사항에 주의를 기울여야 한다.

입력 커패시터를 추가하면 스위칭의 안정성이 향상될 뿐만 아니라 효율 또한 증가한다. <그림8>은 입력 커패시터가 충분히 추가됐을 때 약 1.4%의 효율 향상과 0.3W의 손실 감소가 나타나는 것을 보여준다.

입력측에서 발생하는 링잉(ringing)과 전압 강하는 스위칭 손실을 증가시키는 원인이 된다. 8개의 1206 사이즈 커패시터는 2개의 1210 사이즈 커패시터와 유사한 효율을 보이므로 이 경우 최적의 입력 커패시터 조합은 1210 사이즈의 22㎌ 커패시터 2개가 된다.

입력 커패시터를 선택할 때는 세라믹 커패시터가 가지는 DC 디레이팅(정격 용량 저하) 특성도 함께 고려해야 한다.

예를 들어 12V 조건에서 1206 커패시터와 1210 커패시터의 DC 디레이팅을 비교하면 1206 사이즈가 더 크게 열화된다. <표2>에서는 2개의 무라타(Murata) 커패시터를 예시로 제시하고 있다. 따라서 저전압 고전류 전원 공급용 DC-DC 컨버터에서 입력 커패시터로는 1210 사이즈를 사용하는 것이 권장된다.

![[그림7] 입력 리플 및 스위칭 파형: 상단은 작은 CIN 조합, 하단은 큰 CIN 조합 [제공=ADI]](https://cdn.epnc.co.kr/news/photo/202508/321281_326357_4927.jpg)

총 입력 커패시턴스가 작을 경우(그림7의 상단 파형) 중부하 조건에서 SW 노드 파형에 큰 링잉이 발생한다. 이는 상단 스위치가 도통될 때 대부분의 전류가 입력 커패시터로부터 공급되기 때문이다.

총 전하량은 커패시턴스에 전압을 곱한 값(Q=CV)으로 계산되며 커패시턴스가 작을수록 CIN에서의 전압 강하가 커진다. 이 CIN과 입력 트레이스 및 IC 패키지의 기생 인덕턴스가 함께 LC 탱크 회로를 형성하게 되고 이로 인해 스위칭 노드에서 링잉이 발생한다.

전압 강하가 클 경우에는 SW 파형이 왜곡되고 작은 펄스 뒤에 큰 펄스가 나오는 등 스위칭 불안정성도 유발된다.

스위칭의 이러한 불안정성은 더 많은 입력 커패시턴스를 추가해 링잉을 억제함으로써 개선할 수 있다. 작은 CIN 조합과 비교할 때 큰 CIN 조합은 총 커패시턴스 값을 2배로 증가시킨다.

입력 커패시터가 상단 스위치에 가깝게 배치될수록 이러한 효과는 더 크게 나타난다. 따라서 패키지 내부 커패시터의 용량을 늘리는 것이 바람직하다.

이 예시에서는 0.1㎌(0402, X8L) 커패시터 2개를 0.22㎌(0402, X7R) 용량의 제품으로 교체했고(표1 참조) 이로 인해 스위칭이 안정적으로 변했다(그림7 하단 파형 참조).

![[그림8] 다양한 CIN 조합에 따른 효율 및 손실 vs. 부하 전류 [제공=ADI]](https://cdn.epnc.co.kr/news/photo/202508/321281_326358_5037.jpg)

![[표2] 무라타 커패시터 비교 [제공=ADI]](https://cdn.epnc.co.kr/news/photo/202508/321281_326360_5117.jpg)

SIMPLIS 시뮬레이션은 엔지니어가 최적의 CIN 값을 설계하는 데 유용한 도구가 될 수 있다.

<그림9>는 전원 트레이스에 존재하는 기생 인덕턴스를 추정해 구성한 벅 레귤레이터 회로를 보여준다. 입력 커패시턴스는 12V 입력 전압에서 세라믹 커패시터의 DC 디레이팅을 고려해 조정됐다. 입력 커패시턴스를 2×70nF에서 2×140nF로 2배로 증가시키면 링잉 현상이 개선된다(그림10).

![[그림9] SIMPLIS 시뮬레이션 회로도 [제공=ADI]](https://cdn.epnc.co.kr/news/photo/202508/321281_326361_5149.jpg)

결론

이 글은 저전압 고전류 전원 공급 설계에 중점을 두고 특히 중부하 조건에서 효율을 향상시키기 위한 2가지 방법을 소개했다.

첫째, 스위칭 노드의 열화상에서 확인된 바와 같이 해당 영역은 IC와 거의 동일한 수준의 온도 상승을 보인다. 이에 따라 인덕터 방향을 바꿔 스위칭 노드의 트레이스 길이를 줄이면 손실을 줄일 수 있다는 점을 권장한다.

둘째, 입력 커패시턴스 설계는 매우 중요하지만 자주 간과되기 쉽다. 입력 커패시턴스가 부족할 경우 전원 공급의 불안정성과 비효율을 초래할 수 있다. 따라서 저전압 고전류 전원 설계를 수행하는 애플리케이션 엔지니어는 입력 커패시턴스의 용량을 적절히 조절해 안정성과 효율을 모두 확보할 수 있도록 주의 깊게 접근해야 한다.

![[그림10] 시뮬레이션 결과(상단: CIN=2×70nF, 하단: CIN=2×140nF) [제공=ADI]](https://cdn.epnc.co.kr/news/photo/202508/321281_326362_5223.jpg)

그래도 삭제하시겠습니까?