초광대역 출력 전압을 갖는 LED 드라이버용

이 글은 FL7733을 이용해 초광대역 출력 전압 범위를 갖는 싱글스테이지 플라이백 LED 드라이버를 위한 실용적인 설계 고려 사항을 제시하는데, 여기에는 변압기 설계 및 핵심 부품 선택 절차가 포함된다. 설계 절차는 실험용 프로토타입 컨버터를 통해 검증된다.

고휘도 LED의 지속적인 효율 향상으로 인해, 점점 더 많은 수의 조명 램프가 백열등, 형광등, 평판, 다운라이트 등의 대체품으로 LED를 이용한 설계가 이루어지고 있습니다. LED 드라이버에는 매우 정밀한 출력 전류 제어가 필요한데, 이는 LED 휘도와 컬러가 LED 전류 레벨에 의해 좌우되기 때문입니다.

이와 동시에 고역률(PF)과 낮은 고조파 왜곡율(THD)이 LED 드라이버에 대한 주요 설계 요건이 되고 있습니다. 정밀 출력 전류 제어가 필요한 어플리케이션에 기존에는 2차측의 전류 감지를 이용하는 제어 방법(SSR)을 이용하였는데, 이 경우 추가적인 감지 손실이 발생합니다.

LED 드라이버를 위한 1차측 제어(PSR)는 솔리드 스테이트 라이팅(SSL) 제품에 대한 국제 규격(예: Energy Star)을 만족하는 데 있어 하나의 해결책이 될 수 있습니다. PSR은 파워 서플라이의 1차측 정보만으로 정밀하게 출력 전류를 제어하여, 출력 전류 감지 손실을 막고 2차 피드백 회로를 없애줍니다. 그러면 작은크기의 램프 내부에 드라이버 회로를 내장할 수 있으며 SSL 어플리케이션에 대한 국제 규정을 추가 비용 없이도 충족시킬 수 있습니다.

페어차일드의 Pulse Width Modulation(PWM) PSR컨트롤러인 FL7733은 외부 추가 부품 없이도 SSL 규격을 쉽게 충족할 수 있게 해 줍니다. FL7733은 변압기의 자화 인덕턴스 변화, 입력 및 출력 전압 변화 시에도 매우 정밀하게 출력 전류를 제어하며, 시스템 신뢰도를 위한 강력한 보호 기능을 제공합니다.

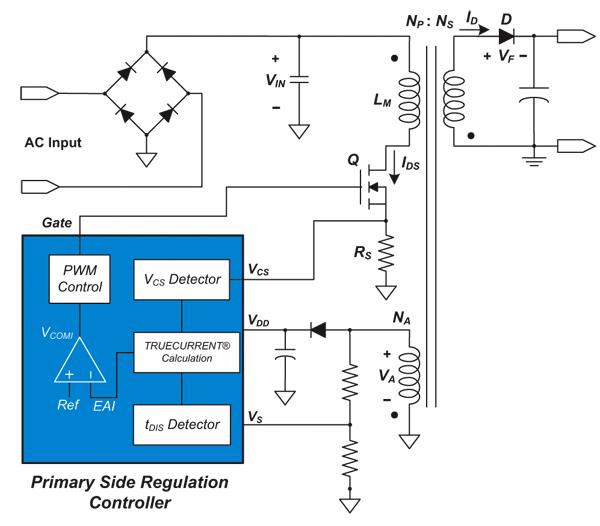

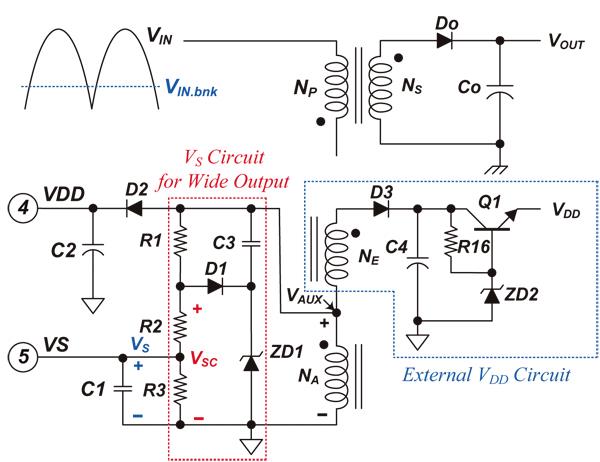

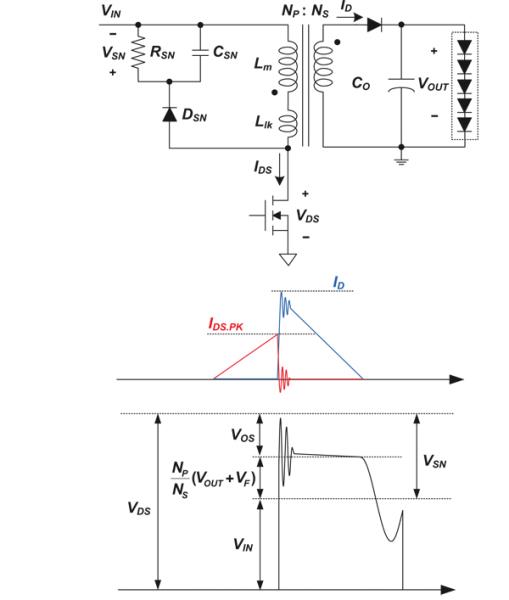

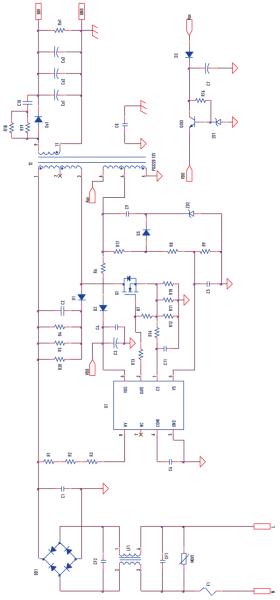

이 글은 FL7733을 이용해 초광대역 출력 전압 범위를 갖는 싱글스테이지 플라이백 LED 드라이버를 위한 실용적인 설계 고려 사항을 제시하는데, 여기에는 변압기 설계 및 핵심 부품 선택 절차가 포함됩니다. 설계 절차는 실험용 프로토타입 컨버터를 통해 검증됩니다. 그림 1은 FL7733을 이용해 1차측에서 제어되는 플라이백 LED 드라이버의 일반적인 응용 회로를 보여줍니다.

1차측 제어의 동작 원리

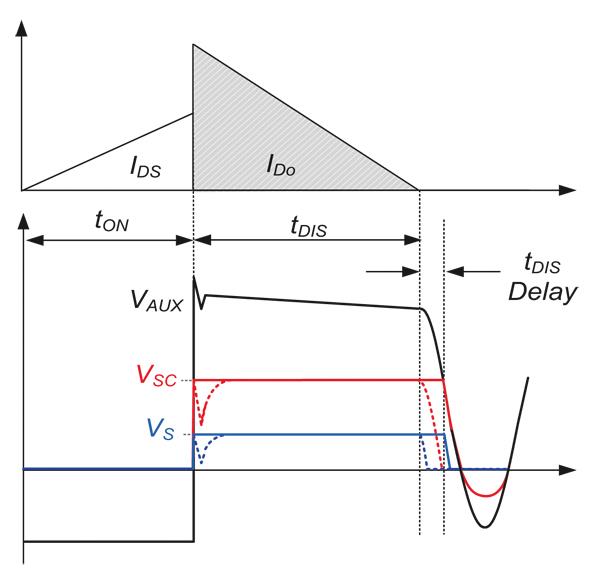

일반적으로, 싱글스테이지 1차측 제어 플라이백 컨버터에는 전류 불연속 모드(DCM) 작동이 선호되는데, 이 모드에서 작동할 경우 더 나은 출력 제어, 더 높은 PF 및 더 낮은 THD를 실현할 수 있기 때문입니다. DCM 플라이백 컨버터의 작동 원리는 다음과 같습니다.

모드 I

MOSFET이 턴온 (tON) 되는 동안, 입력 전압(VIN)은 변압기의 1차측 인덕턴스(Lm)에 인가됩니다. 그러면, MOSFET의 드레인 전류(IDS)는 0에서 피크값(IDS.PK)까지 그림 3에서처럼 선형적으로 증가합니다. 이 시간 동안, 입력 에너지가 인덕터에 저장됩니다.

모드 II

MOSFET (Q)이 꺼지면, 변압기에 저장된 에너지로 인해 정류기 다이오드 (D)가 켜집니다.

다이오드가 전도 상태인 동안에는, 출력 전압(VOUT)과 다이오드 순방향 전압 강하(VF)가 변압기의 2차측 인덕턴스에 인가되고 다이오드 전류(ID)가 피크값(IDS.PK NP/NS)에서 0으로 선형적으로 감소합니다. 인덕터 전류 방전 시간(tDIS)이 끝나면, 변압기에 저장된 모든 에너지가 출력으로 전달됩니다.

모드 III

다이오드 전류가 0에 도달하면, 변압기 보조 권선 전압이 1차측 인덕턴스(Lm)와 MOSFET (Q)의 기생 커패시터에 의해 공진하기 시작합니다.

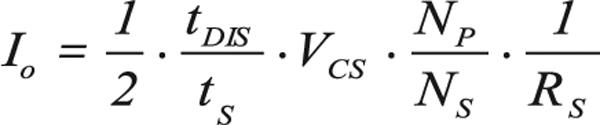

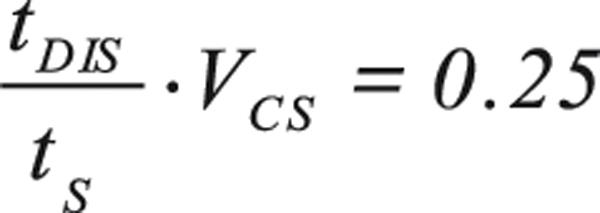

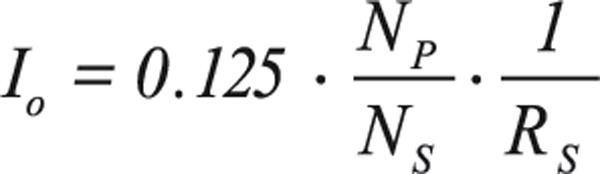

출력 전류는 피크 드레인 전류와 인덕터 전류 방전 시간을 통해 추산할 수 있는데, 출력 전류가 정상 상태에서 다이오드 전류의 평균과 같기 때문입니다. 드레인 전류의 피크값은 CS 피크 전압 검출기를 통해 감지되고 인덕터 전류 방전 시간(tDIS)은 tDIS 검출기에 의해 감지됩니다. 피크 드레인 전류, 인덕터 전류 방전 시간 및 동작 스위칭 주기 정보를 통해 혁신적인 TRUECURRENTⓡ 계산 블록이 다음과 같이 출력 전류를 추산합니다.

설계 절차

싱글스테이지 플라이백 LED 드라이버의 설계 절차는 FL7733을 기반으로 하며, 참고 자료로 그림 1의 회로를 이용하여 설명하고 있습니다. 50W(50V /1A) 출력을 갖는 절연 LED 드라이버가 설계 예시로 선택되었습니다. 설계 사양은 다음과 같습니다.

•입력 전압 범위: 90 ~ 264VAC 및 50 ~ 60Hz

•출력 전압 및 전류: 50 V / 1.0 A

•출력 전압 범위: 7 V ~ 55 V

•최소 효율: 88%

•동작 스위칭 주파수: 65 kHz

•최고 듀티: 40%

1단계. 변압기 1차측 인덕턴스 선택(Lm)

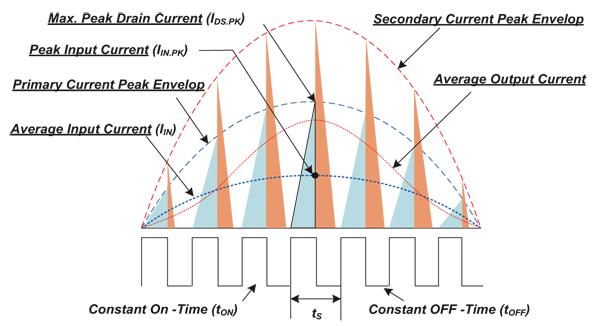

FL7733은 일정한 켜짐 및 꺼짐 시간으로 작동합니다(그림 4 참조). MOSFET 켜짐 시간(tON) 및 스위칭 주기(tS)가 일정하면 입력 전류가 입력 전압에 비례하여 고역률을 달성할 수 있습니다.

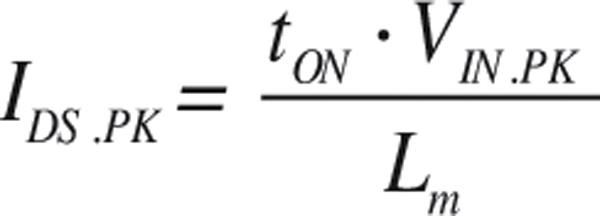

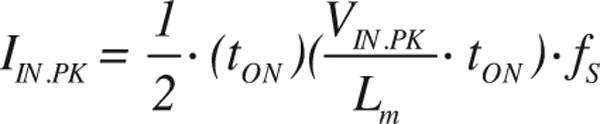

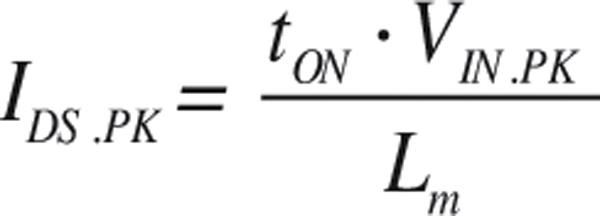

FL7733을 이용하는 싱글스테이지 플라이백은 일정한 온타임(tON)과 스위칭 타임 tS로 DCM에서 작동하는 것으로 가정합니다. 입력 전압이 tON동안 자화 인덕턴스(Lm)에 인가되면서 자기 에너지를 충전합니다. 따라서 MOSFET의 최대 피크 변환 전류(IDS.PK)는 라인 전압의 피크 포인트에서 발생합니다(그림 4 참조). 피크 입력 전류(IIN.PK) 또한 라인 사이클의 피크 입력 전압에서 보입니다. 최대 tON이 결정되고 나면, 다음과 같이 MOSFET의 IDS.PK를 최소 라인 입력 전압과 최대부하 조건에서 구할 수 있습니다.

여기서 VIN.PK와 tON은 각각 최소 라인 입력 전압에서의 피크 입력 전압과 최대 켜짐 시간입니다.

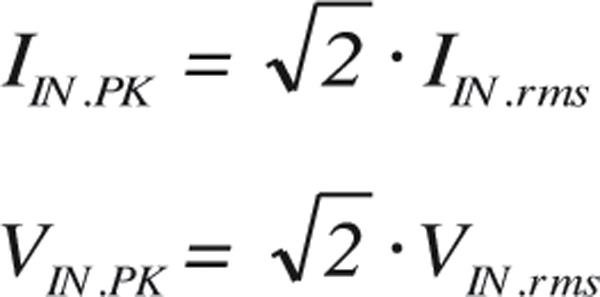

방정식 (4)를 이용하면 다음을 통해 피크 입력 전류가 구해집니다.

그러면, IIN.PK와 VIN.PK를 다음과 같이 나타낼 수 있습니다.

여기서 IIN.rms와 VIN.rms는 각각 rms 라인 입력 전류와 전압입니다.

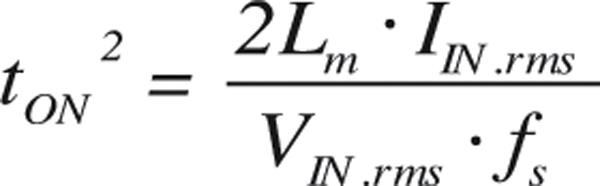

필요한 Lm 값을 계산하려면 tON이 필요합니다. 방정식 (5)~(7)을 이용해 다음과 같이 켜짐 시간, tON을 구합니다.

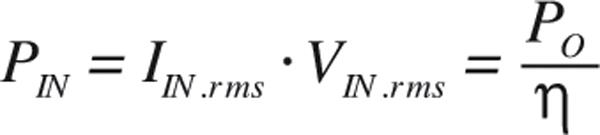

입력 전력은 다음과 같이 주어집니다.

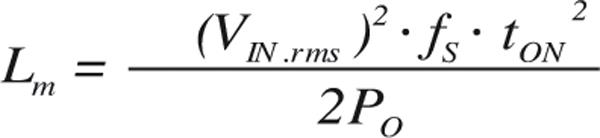

방정식 (8) 및 (9)를 이용해 다음과 같이 Lm 값을 구합니다.

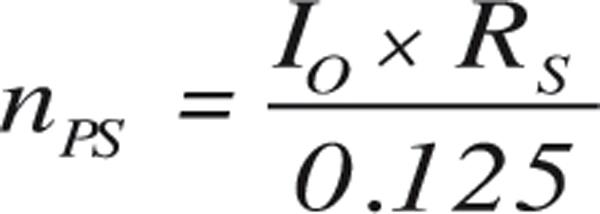

2단계. 센싱 레지스터와 권선비 nPS 선택

FL7733은 TRUECURRENTⓡ 계산 방법을 채택하는데, 이 방법은 일정한 출력 전류(IO) 제어를 위한 방법으로, 방정식 (1)에 정의된 바와 같습니다. 출력 전류는 변압기의 1차와 2차 간 권선비 nps에 비례하고 센싱 레지스터 값(RS)에 반비례합니다. FL7733은 LED 단락 또는 과부하로부터 시스템을 보호하기 위해 VCS를 검출하여 사이클별 전류 제한을 수행합니다.

따라서, VCS 레벨은 전류 제한 보호 기능이 켜지지 않고 정격 시스템 전력을 처리해야 합니다. 사이클별 제한 레벨(typical: 0.85 V)은 전부하 조건에서 CS 피크 전압(VCS.PK)보다 15~20% 높게 설정되는 것이 일반적입니다. MOSFET 피크 전류(ISW.PK)는 다음과 같이 VCS,PK로 변환됩니다.

방정식 (3)에 따라, 1차 대 2차 권선비는 다음과 같이 센싱 레지스터와 출력 전류에 의해 결정됩니다.

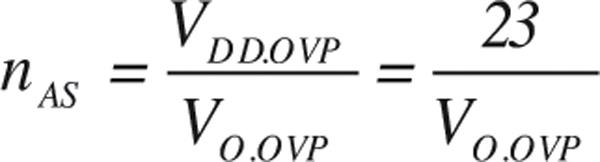

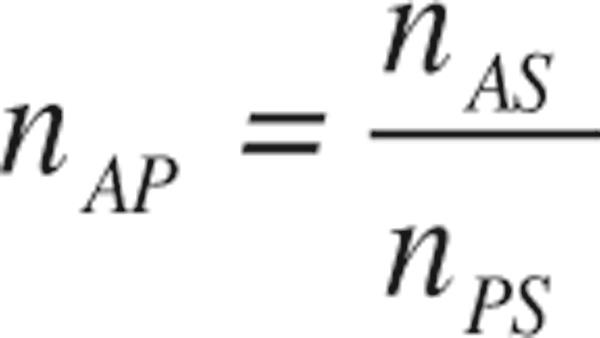

3단계. nAS와 nAP 선택

VDD 전압이 23V이면, FL7733은 과전압 보호(OVP)로 인해 스위칭 작동을 중지합니다. 따라서, nAS와 nAP는 다음과 같이 결정될 수 있습니다.

여기서, nAS는 보조 대2차 권선비이고 nAP는 변압기의 보조 대 1차 권선비입니다.

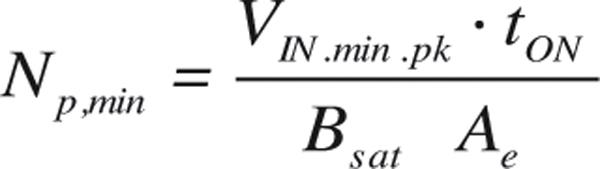

4단계. 변압기 설계

1차 권선 수는 패러데이의 법칙으로 결정됩니다. Np,min은 1차 권선 에 인가되는 최소 라인 입력 전압의 피크값과 최대 온타임(on time)에 의해 정해집니다. 코어 포화를 막기 위한 변압기 1차측 최소 권수는 다음과 같습니다.

여기서 Ae는 코어의 횡단면적(mm2)이고 Bsat는 포화 자속 밀도(Tesla)입니다.

온도가 올라가면 포화 자속 밀도는 감소하기 때문에, 변압기가 밀폐 케이스 내부에 사용되는 경우 고온 특성을 고려해야 합니다.

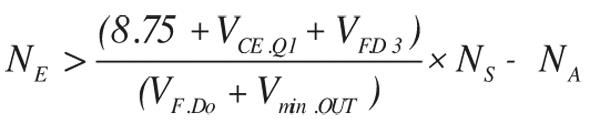

FL7733의 VDD 동작 범위는 8.75~23V이므로, MOSFET 스위칭은 출력 전압이 VOUT-UVLO(8.75 ×NS /NA)보다 낮은 경우 UVLO를 터치하여 작동이 중지됩니다. 따라서, VDD는 광대역 출력 전압 범위 7~55V 전체에 걸쳐 UVLO를 일으키지 않고 올바르게 공급되어야 합니다. VDD는 외부 권선 NE와 전압 레규레이터로 구성된 VDD 회로를 추가하여 공급될 수 있습니다(그림 5 참조). NE는 VDD가 최소 출력 전압(Vmin.OUT)에서 UVLO를 일으키지 않고 공급될 수 있도록 설계되어야 합니다. 외부 권선 NE는 다음과 같이 결정될 수 있습니다.

여기서 VCE.Q1은 Q1의 컬렉터-이미터 간 포화 전압이고, VF.D3는 D3의 순방향 전압이며, VF.Do는 최소 출력 전압에서 Do의 순방향 전압입니다.

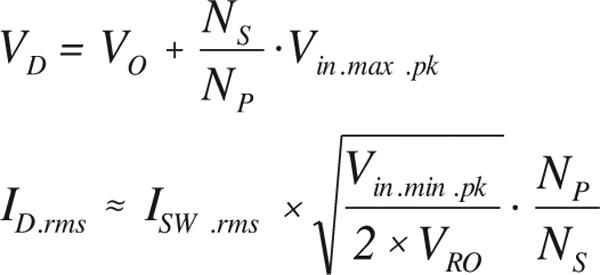

5단계. 광대역 출력 범위를 위한 VS 회로

R1, R2 및 R3 선택 시 첫 번째 고려 사항은 정격 전력에서 65kHz 스위칭 주파수로 동작하기 위해서 다이오드 전류 전도 시간이 끝날 때 VS가 2.45V여야 하는 것 입니다. 두 번째 고려 사항은 VS 블랭킹입니다(아래에서 설명). 출력 전압은 보조 권선과 VS 핀에 연결된 저항성 디바이더에 의해 검출됩니다(그림 5 참조).

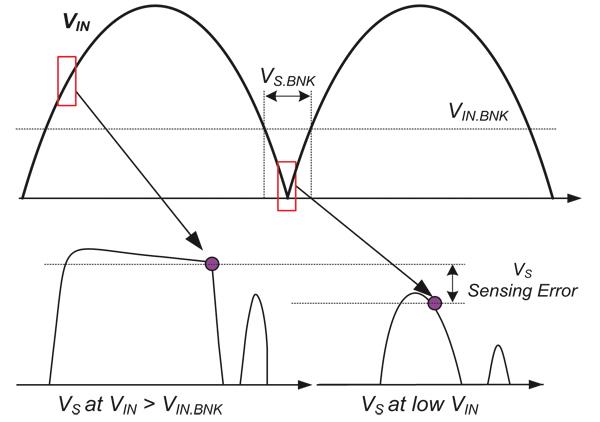

그러나, DC 링크 커패시터가 없는 싱글스테이지 플라이백 컨버터에서는 작은 Lm 전류로 인해 보조 권선 전압은 전 입력전압 조건에 걸친 출력 전압이 반영된 전압을 클램핑할 수 없습니다. 여기에는 VS 전압 감지 오류가 포함됩니다(그림 6 참조). 주파수는 라인 전압 제로 크로싱 부근에서 빠르게 떨어지는데, 이는 LED 광플리커 현상을 야기할 수 있습니다. 전입력 라인 전압에 걸쳐 일정한 주파수를 유지하기 위해, 라인 전압이 보조 권선을 감지하여 특정 레벨 이하가 되면 VS 블랭킹이 VS 샘플링을 비활성화합니다.

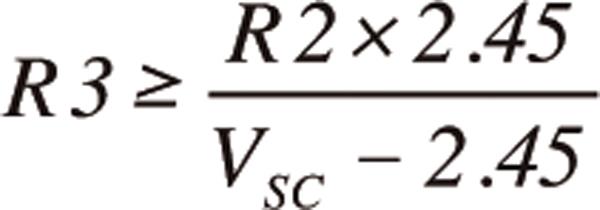

광대역 출력 애플리케이션에서, 정상 조건의 VS 레벨은 SLP와 VS OVP를 일으키지 않도록 0.6 ~ 3V를 유지해야 하는데, 이것은 추가 VS 회로를 이용하면 가능합니다(그림 5 참조).

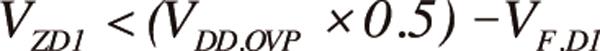

높은 스위칭 주파수, 50% 이하의 정격 출력 전압 및 VIN.bnk에 대한 VS 블랭킹 레벨을 고려할 때, 다음과 같이 Zener 다이오드 전압(VZD1), R1, R2 및 R3을 구할 수 있습니다.

VF.D1는 Zener 다이오드 ZD1과 직렬로 연결된 D1의 순방향 전압입니다.

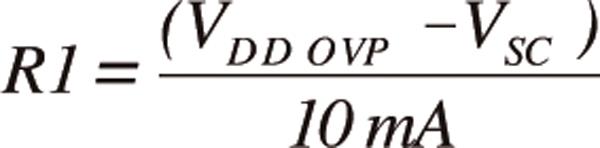

Zener 다이오드 제어 범위와 그 정격 전력을 고려할 때, Zener 다이오드 전류 IZD1을 10mA로 제한하기 위해 R1을 선택할 수 있습니다.

여기서 VSC는 D1 및 ZD1에 의해 클램핑된 전압입니다.

여기서 VIN.bnk는 VS 블랭킹에 대한 라인 전압 레벨이고 IVS.bnk는 VS 블랭킹에 대한 전류 레벨입니다.

스위칭 노이즈를 바이패스 하기 위해 5 ~ 10pF 정도의 바이패스 커패시터 C1을 VS와 GND 핀 사이에 가까이 위치하는 것이 좋습니다. 커패시터의 값이 정전류 제어에 영향을 미칠 수 있기 때문입니다. 과도하게 높은 VS 정전용량이 선택되면, 소형 VS 커패서터에 비해 방전 시간(tDIS)이 길어지고 출력 전류는 낮아집니다.

광대역 출력 전압 범위에 대한 VS 회로에서 추가로 고려할 사항은 보조 권선에 걸친 Vaux가 VSC에 클램핑될 때 VAUX와 VSC 간의 전압 차에 의해 발생하는 tDIS 지연입니다(그림 7 참조). 이러한 지연은 VAUX가 VSC와 같아질 때까지 계속되는데, 이는 일정 출력 전류 제어에 영향을 미칠 수 있습니다. 보조 권선과 Zener 다이오드 ZD1 사이에 커패시터 C9를 놓으면 이런 지연 현상을 없앨 수 있습니다.

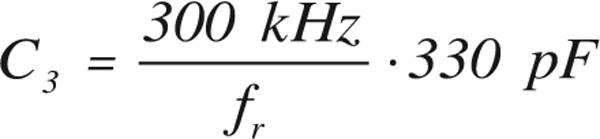

게이트가 꺼져 있을 때는 VAUX가 커패시터 전압 VC3 및 VZD1으로 나누어집니다. 그러면 그때 VC3는 방전 없이 해당 전압으로 유지되지만 VZD2는 다이오드 전류 ID가 0에 도달하면 VAUX - VC3로 감소됩니다. 따라서 VS는 VAUX를 따라갈 수 있습니다(그림 7에 나타난 점선 참조). C3는 자화 인덕턴스 Lm과 MOSFET COSS 간의 공진에 의해 결정된 공진 주파수에 따라 적절한 값으로 선택되어야 합니다. 이 어플리케이션에 사용된 330pF는 시행착오를 거쳐 선택된 것입니다. 그 값은 다음과 같이 구해질 수 있습니다.

여기서 fr은 COSS와 Lm 간의 공진에 의해 결정된 공진 주파수입니다.

6단계. 스위칭 소자의 전압과 전류 계산

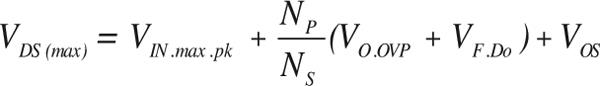

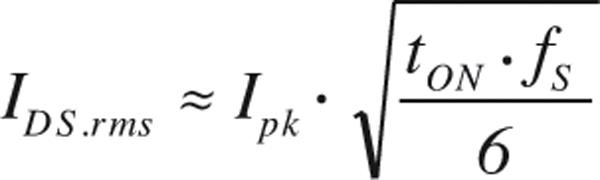

1차측 MOSFET: MOSFET의 전압 스트레스는 변압기 권선비 결정에서 다룹니다. 드레인 전압 오버슈트가 특정 전압 VOS로 간주된다고 가정하면, 최대 드레인 전압은 다음과 같습니다.

2차측 다이오드: 최대 역방향 전압과 정류기 다이오드의 rms 전류는 다음과 같이 구해집니다.

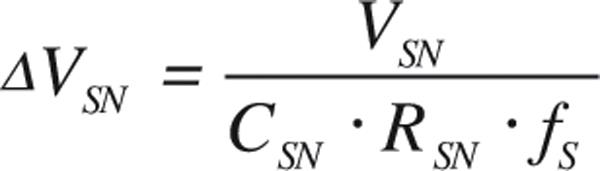

7단계. 1차측의 RCD 스너버 설계

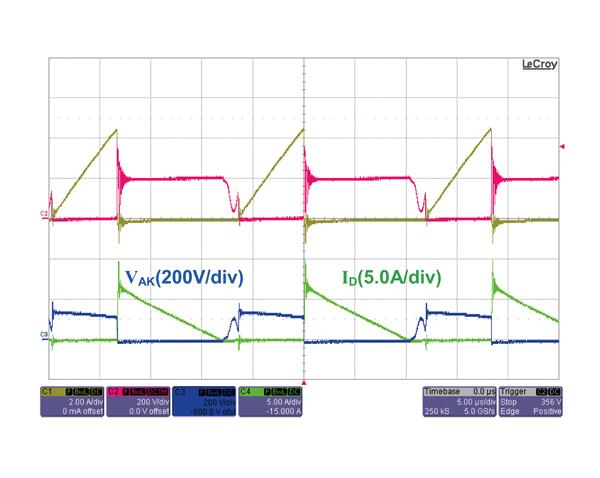

전력 MOSFET이 꺼지면 변압기 누설 인덕턴스로 인해 드레인에 고전압 스파이크가 발생합니다. MOSFET의 과전압은 아발란치 항복으로 이어질 수 있고 결국 소자가 고장나게 됩니다. 따라서 전압을 클램핑하기 위해 추가 네트워크를 사용해야 합니다. RCD 스너버 회로와 그 파형은 그림 8에 나타나 있습니다.

MOSFET 드레인 전압이 스너버 다이오드의 캐소드 전압을 초과하면 스너버 다이오드(DSN)를 켜서 RCD 스너버 네트워크가 누설 인덕턴스의 전류를 흡수합니다. 스너버 네트워크의 분석에서는 스너버 커패시터가 충분히 커서 그 전압이 한 스위칭 사이클 동안 크게 변화하지 않는다고 가정합니다. 스너버 커패시터는 세라믹 또는 낮은 ESR을 제공하는 소재로 되어 있어야 합니다. 이에 따라 전해 또는 탄탈 커패시터는 사용할 수 없습니다.

최대 부하 상태에서 스너버 커패시터 전압은 다음과 같습니다.

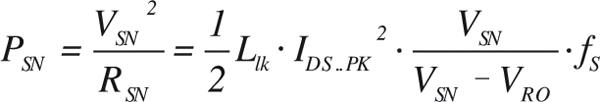

스너버 네트워크에서의 소비 전력은 다음과 같이 구해집니다.

여기서 Llk는 누설 인덕턴스이고 VSN은 최대 부하에서의 스너버 커패시터 전압이며 RSN은 스너버 저항입니다.

누설 인덕턴스는 다른 모든 권선을 단락 시킨 후 1차 권선의 스위칭 주파수에서 측정됩니다. 정격 파워에 적절한 스너버 저항은 전력 손실을 기반으로 선택되어야 합니다. 스너버 커패시터 전압의 최대 리플은 다음과 같이 구해집니다.

일반적으로는 선택된 커패시터 전압의 5 ~ 20%의 리플이 적당합니다. 이 스너버 설계에서는, 인덕터의 방전 손실이나 부유 정전용량은 둘 다 고려되지 않습니다.

PCB 레이아웃 지침

높은 기생 인덕턴스 또는 저항이 있는 PCB 레이아웃은 심각한 스위칭 노이즈를 유발할 수 있고 시스템 불안정의 원인이 될 수 있기 때문에 전력 컨버터를 위한 PCB 레이아웃은 회로 설계만큼이나 중요합니다. PCB는 제어 신호에 스위칭 노이즈가 커플링 되는 것을 최소화하도록 설계되어야 합니다.

1. 시그날 그라운드와 파워 그라운드는 그라운드 루프 노이즈를 방지하기 위해 한 위치(GND 핀)에서 분리하여 연결해야 합니다. 브리지 다이오드에서 센싱저항까지의 파워 그라운드 경로는 짧고 넓어야 합니다.

2. 게이트 구동 전류 경로(GATE - RGATE -MOS FET - RCS - GND)는 가능한 한 짧아야 합니다.

3. 제어 핀 부품(예: CCOMI , CVS 및 RVS2)은 할당된 핀 및 신호 접지와 가까워야 합니다.

4. MOSFET 드레인과 및 RCD 스너버의 관련된 고전압 트레이스는 불필요한 간섭을 피하기 위해 제어 회로에서 멀리 떨어뜨려 놓아야 합니다.

5. MOSFET에 히트 싱크가 사용되는 경우, 이 히트 싱크를 파워그라운드에 연결합니다.

6. 보조 권선 접지는 제어 핀 구성품의 접지보다 GND 핀에 가까이 연결되어 있어야 합니다.

연구용 노트

파워 서플라이를 수정하거나 납땜/납땜 제거하기 전에 외부 블리딩 레지스터를 통해 1차 커패시터를 방전합니다. 그렇지 않으면 PWM IC가 프로세스 중에 외부 고전압에 의해 손상될 수 있습니다. 이 소자는 정전기 방전(ESD)에 민감합니다. 수율을 향상시키기 위해 생산 라인에서는 ANSI ESD S1.1, ESD S1.4, ESD S7.1, ESD STM 12.1 및 EOS/ESD S6.1 표준에 규정된 대로 ESD 보호를 수행해야 합니다.

설계 도해 예시

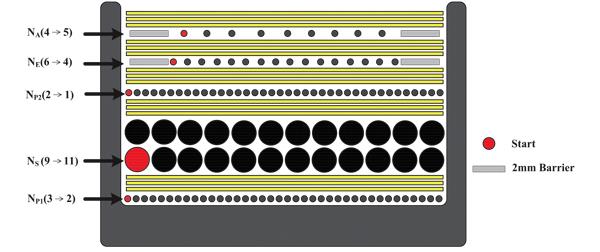

그림 10은 50W LED 드라이버 설계 도해의 예시를 보여줍니다. PQ3220 코어는 변압기에 사용됩니다. 그림 11은 변압기 정보를 보여줍니다.

설계 예시 실험 결과

이 애플리케이션 노트에 제시된 설계 절차의 타당성을 증명하기 위해, 설계 예시에 설명된 컨버터를 테스트했습니다.

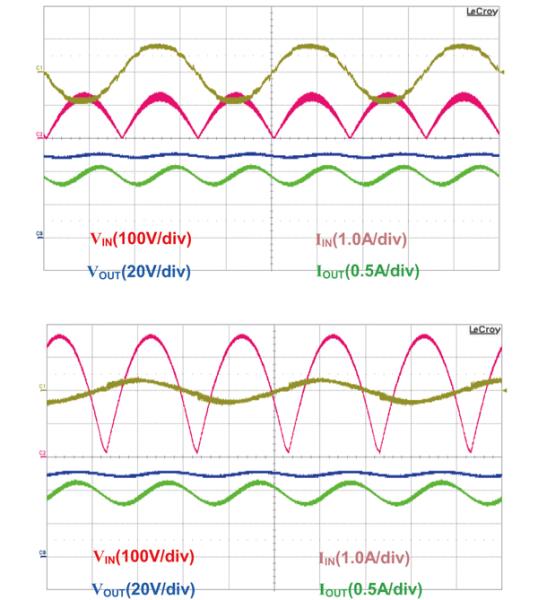

0는 최소 및 최대 라인 전압 조건에서 정상 동작 파형을 보여줍니다. 입력 전류 파형은 사인파이며 높은 PF와 낮은 THD 성능은 DCM 제어를 통해 달성될 수 있습니다.

그림 13은 최소 입력 조건에서의 주요 파형을 보여줍니다. STEP-1에서 설계된 변압기 인덕턴스에 대한 전도 시간과 드레인 피크 전류는 각각 6.2와 4.5A입니다.

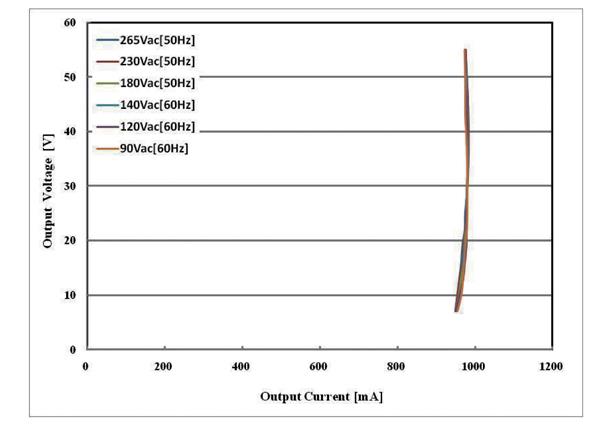

그림 14는 전체 라인 및 출력 전압 범위에서 측정된 CC 공차를 보여줍니다. 정격 출력 전압에서 유니버설 라인에 대한 CC는 ±0.3% 미만이며, 전체 라인과 초광대역 출력 전압 범위(7V ~ 55V)에 대한 총 CC 조정은 ±1.76%입니다.

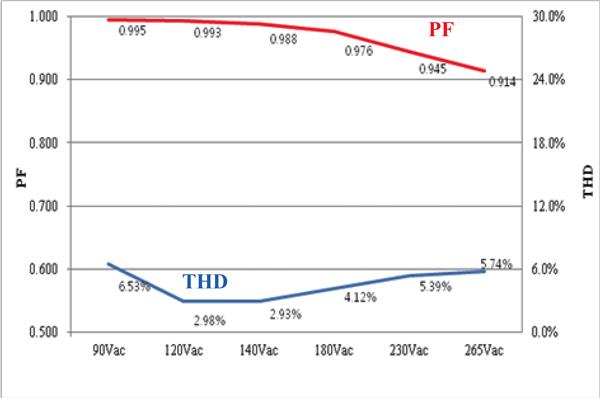

그림 15는 정격 부하 조건에서 측정된 PF와 THD를 보여줍니다. PF는 0.9를 넘어갈 수 있으며 THD는 유니버설 라인 조건에서 7%미만이 될 수 있습니다.

관련 자료

FL7733 - 역률 보정이 지원되는 1차측 제어 LED 드라이버

FEBL052 - 50W LED 드라이버(PFC PSR 플라이백)의 FEBFL7733_L52U050A 평가 보드에 대한 사용 안내서

그래도 삭제하시겠습니까?