반도체 스케일링 한계 돌파를 위한 기술 개발 동향

[테크월드=선연수 기자] 지난해 일본 수출규제 상황으로 인해 국내 소재·부품·장비(이하 소부장) 업계는 1년이 넘는 기간 동안 꾸준히 소부장 자립화·수입 다변화를 꾀하고 있다. 특히, 메모리 반도체 분야는 새로운 소재 없이는 기술적으로 한계가 있는 상황이다.

국제반도체장비재료협회(SEMI)는 지난 19일부터 20일 양일간 SEMI 코리아 2020(SEMI Korea 2020) 행사를 통해 반도체 전자재료 시장의 현 상황과 해결 과제를 논하는 자리를 가졌다.

“차세대 반도체 메모리 디바이스를 위한 새로운 재료”

서울대학교 재료공학부 황철성 교수

첫 발표 연사로 나선 서울대학교 재료공학부 황철성 교수는 “메모리 반도체의 집적도는 계속 높아지고 성능도 계속 향상되고 있다. NAND 플래시의 경우 스케일링 기술이 2019년부터 진전이 없는 상황이다. 현재 새로운 스케일링 방법을 찾는 단계로, 리니어(Linear) 스케일링은 거의 끝났고 구조나 소재를 바꾸는 게 필요하다”고 설명했다.

반도체는 유전율이 높을수록 전하를 많이 저장할 수 있는데, 이를 구현하기 위해서는 새로운 소재가 필요한 상황이다. 황 교수는 D램의 경우 캐패시터 노드의 한 쪽만 사용하면 노드 간 간격이 늘어나게 되면서, 물리적인 두께 문제로 쓸 수 없었던 물질을 사용할 수 있게 된다며 구조적인 혁신을 통해서도 해결할 수 있다고 소개했다.

황 교수는 D램의 리니어 스케일링 한계는 9~10nm 정도로, 2025년쯤에는 현재의 기술에 한계가 올 것으로 예상했다. 이어 “특히, D램은 낸드 플래시보다 트랜지스터 성능이 훨씬 좋아야 하기 때문에 구현 기술이 훨씬 어렵다. 현재가 스택 D램에 대한 연구를 진행해야 할 시기”라고 말했다.

낸드 플래시의 경우 400~500층 사이의 적층 단계에서 더 이상 쌓지 못할 가능성이 높다고 설명했다. 높이를 마냥 높일 수 없기에 셀 간 간격을 줄여야 하는데, 이 경우 터널링에 의한 데이터 손실이 일어나게 된다. 약 400층의 적층 기술이 6~7년 후에는 달성될 것으로 예상되며 새로 찾아올 한계에 대비해야 한다.

메모리 반도체 분야에서 대체 기술로 주목 받는 것으로는 IGZO(Indium Gallium Zinc Oxide)와 ZTO(Zinc-tin Oxide)가 있다. 이를 활용한 테스트가 진행되고 있지만, 아직 해결해야 할 부분이 많다. 황 교수는 “기존의 실리콘(Si) 반도체는 밴드갭이 작아 여러 방법으로 N타입 반도체 홀을 유도할 수 있었으나, IGZO는 아직 그럴 수 있는 방법이 없다. 이레이즈(Erase)의 경우에는 채널 인버젼(Inversion)이 되지 않는 문제도 있다. 전압을 증가시켜도 전자를 빼낼 수 없는 문제나 공정 문제 등을 위한 근본적인 해결이 필요한 상황”이라고 밝혔다.

“디지털 R&D”

PwC 한국 컨설턴트/디렉터 김대현 이사

PwC 컨설팅(PricewaterhouseCoopers Consulting) 한국 김대현 이사는 디지털 R&D가 필요한 이유에 대해 발표했다. 공장 운영의 측면에서는 기존에 쌓아온 데이터를 어떻게 통합해 유의미한 데이터를 얻을까를 고민한다. 이런 스마트팩토리를 구현하기 위해 업계가 디지털 플랫폼을 도입하는 추세다.

김 이사는 “디지털 R&D는 연구원들이 노트에 아이디어를 스케치하는 것조차도 디지털화하는 방향으로 가고 있다”며, “글로벌 화학회사 중에는 연구원들의 연구 노트를 위해 디지털 노트를 제공하고 있으며, 이런 모든 자료들이 저장될 수 있도록 체계를 구축해 나가고 있다”고 덧붙였다.

특히, 대기업은 부서 간 소통 채널이 많이 경직된 경향을 보이기에 R&D를 대기업이 이끌기 어려운 부분이 있다. 해외에서는 오히려 스타트업에서 R&D 디지털화가 많이 이뤄지고 있다. 그러나 최근엔 대기업들도 데이터 플랫폼을 도입하는 경우가 늘고 있다.

또한, 김 이사는 오늘날 기업의 비즈니스 방향이 오로지 고객사에게 맞추는 것이 아닌 기업이 원하는 타깃 모델로 추진하는 쪽으로 발전하고 있어, 디지털 R&D가 더 유용할 것으로 기대했다.

“다가오는 반도체 스케일링 패러다임 변화, 그리고 패터닝과 재료에 미치는 영향”

imec R&D 디렉터 김령한 박사

imec R&D 디렉터 김령한 박사는 반도체 스케일링의 발전 과정을 짚으며 현재 당면한 해결 과제를 발표했다. 스케일링 기술은 초기의 100nm 수준에서는 큰 문제가 없었다. 90nm, 65nm, 40nm를 거쳐 20nm에서 패터닝 해상도 문제와 더블 패터닝 문제가 생겨났다. 14nm에서는 FinFET이 등장하면서 소자의 성능이 개션되고 전력 소모가 줄었으나 복잡성은 증가했다. 10-7nm에서는 멀티 패터닝 문제가 있었으며, 7nm에서는 드디어 EUV 기술이 등장했다.

기술 비용이 상당히 늘어나게 되면서 DTCO(Design Technology Co-Optimization)가 등장했다. 3nm에서는 GAA(Gate-All-Around)라는 혁신 기술이 생겨났고, 향후 2nm에서는 신기술이 공개되거나 GAA 기술 확장 또는 high NA EUV기술의 도래를 기대해볼 수 있다. 이후에는 양자컴퓨팅, 극저온 전자 등의 완전히 새로운 기술 방향으로 갈 수 있다.

DTCO나 새롭게 논의되는 STCO(System Technology Co-Optimization)에서는 디멘셔널 스케일링이 중요하다. 이를 트랜지스터(소자), 나노 인터커넥트, 패터닝 기술로 나눠볼 수 있다.

업계는 DTCO, 디멘셔널 스케일링을 지원하는 STCO(System Technology Co-Optimization)를 논하고 있다. DTCO는 설계가 디멘셔널 스케일링을 지원한다. STCO는 시스템과 패키징을 최적화하고 DTCO와 디멘셔널 스케일링을 지원한다. 디멘셔널 스케일링이 중요하고, 재료가 이 디멘셔널 스케일링에 매우 중요한 역할을 할 것으로 생각된다. 이 기술을 3가지로 나눠보겠다. 첫째는 트랜지스터, 둘째는 뒷단을 위한 나노 인터커넥트, 셋째는 패터닝이다.

그중 패터닝에서 EUV을 살펴보자. 현재 EUV 기술로는 싱글 패터닝, 싱글 노광(Exposure)이 존재하며, 미래 기술로는 EUV 더블 노광, high NA EUV 기술이 있다. 싱글 패터닝에서 더블 패터닝으로 넘어가는 과정에서 ‘Stochastic’ 결함 문제가 발생하는데, 이는 EUV의 고유 특성에 기인한 랜덤 결함이다. 높은 도스와 낮은 처리량의 싱글 패터닝을 유지할 것인지,합리적인 비용으로 높은 처리량과 낮은 Stochastic 결함의 더블 패터닝으로 전환할 것인지에 대한 업계 내 논의가 활발하다고 김 박사는 설명했다.

또한, EUV 더블 패터닝이나 high NA EUV로 가기 위해서는 재료 단계에서의 혁신이 필요한 상황이다. 김 박사는 “레지스트는 다른 재료에 매우 종속적이다. 이는 기판의 재료, 하층 재료, 레지스트를 합쳐 리소 성능을 최적화하는 게 중요하다”고 강조했다.

“반도체 제조를 위한 재료 기술 트렌드”

SK하이닉스 박형순 TL

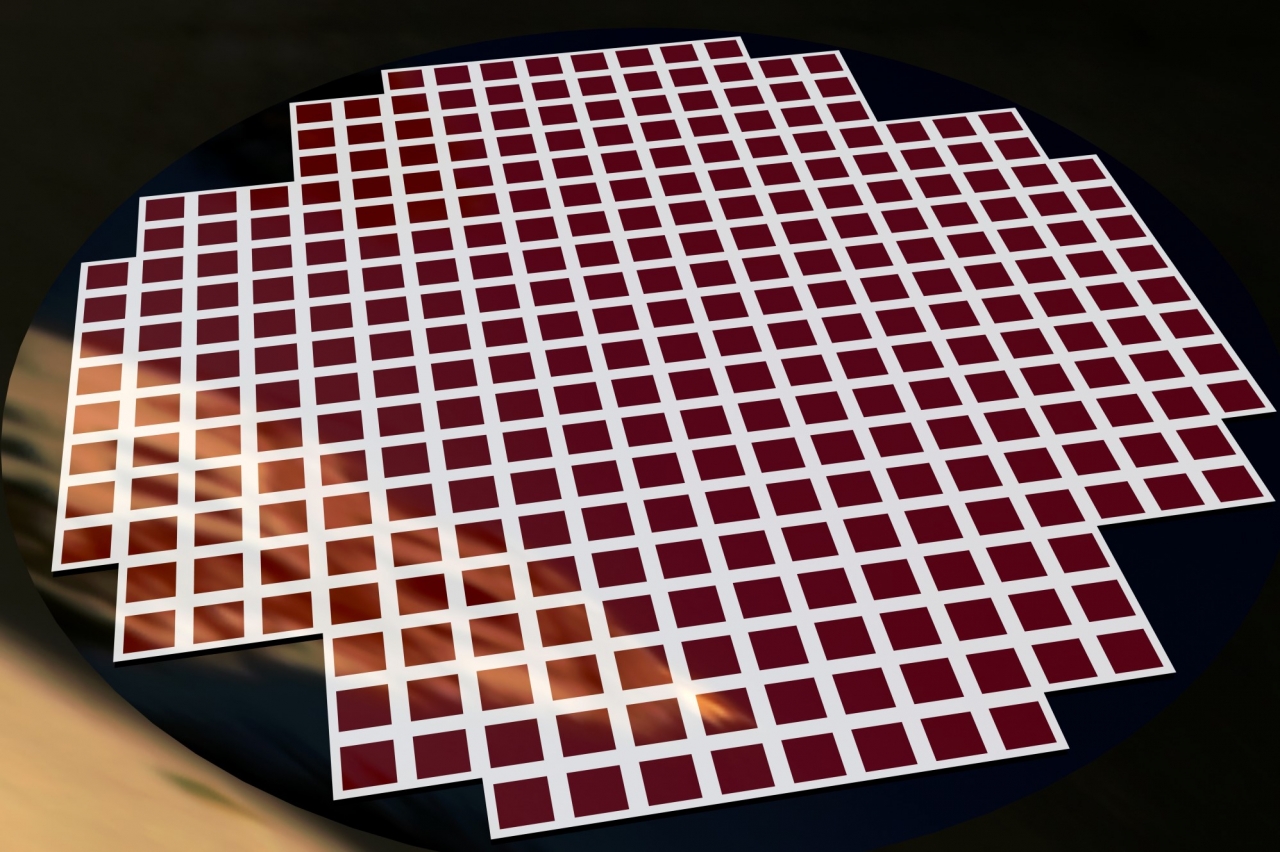

SK하이닉스 박형순 TL은 반도체 소재의 기술적 트렌드에 대해 소개했다. 박 수석은 “제조 공정은 크게 웨이퍼 제조 공정과 패키지·테스트 공정으로 나눠진다. 모든 단계에 소재가 들어가게 되는데, D램의 경우 10nm 이후에 스케일링에서 문제가 커질 것으로 예상된다. 낸드 플래시는 14nm 이후 스케일링이 어려워 3D 낸드 플래시로 전환되는 시점”이라고 밝혔다.

패터닝과 관련해 ArF 기술까지는 로드맵에 맞춰 순조롭게 개발돼 왔다. 그러나 이후에 개발 난항을 겪으며 ArF 이머전(Immersion) 기술이 등장했다. 뒤이어 EUV의 기술 도입이 늦어지면서 SPT 등의 기술이 생겨났고, 현재는 ArF 기술이 여전히 롱런하는 상황이다. EUV의 경우 기술적인 성숙도를 높이는 게 상당히 중요하며, 이를 대체할 기술도 개발되고 있다.

박 수석은 “미세한 공정 차이가 장비에 이상을 일으킬 수 있기에, 이를 방지하기 위해 알고리즘을 고도화해 공정 마진을 확보하려는 노력이 많이 이뤄지고 있다. 칩 메이커, BP사, 장비사 모두가 긴밀히 협력해 진행하는 것이 중요하다”고 말했다.

소재 또한 마찬가지다. 박 수석은 소재의 품질 제어 시스템을 빅데이터와 연계함으로써 머신러닝 기술로 공정과 품질 이상을 크로스 체크하는 방향으로 발전한다면, 소재 측면에서도 획기적으로 발전할 수 있을 것이라고 기대했다.

“반도체 소재 SCM에 관한 지속적인 품질 향상 전략”

삼성전자 메모리 소재 기술 그룹 최삼종 그룹장

삼성전자 메모리 소재 기술 그룹장인 최삼종 박사는 항상성을 갖춘 반도체 소재 공급 품질에 대해 발표했다. 최 박사는 “제품에 적합한 소재는 선제적으로 디자인된 후 전기에 공급돼야 한다”며, “기존에는 가전제품, 데스크톱, 노트북, 스마트폰 등의 고장 정도가 문제였지만, 이제는 자율주행이나 바이오 분야로 반도체 기술이 확장 적용되면서 사람의 생명과 직결된 문제가 발생할 수 있어 품질 관리가 더 중요해졌다”고 설명했다.

고층 빌딩을 만들면 생산 공정과 과정도 늘어날 수 밖게 없다. 점점 높아지는 적층 기술과 미세한 패턴으로 새로운 현상이 많이 발생하고 있으며, 그 문제는 신규 제품에 고스란히 드러난다. 이를 위해 고스택 하드마스크가 필요하고 이 혁신의 기반은 새로운 물질을 찾는 것이다.

최 박사는 “기존에는 소재의 특성, 품질, 아웃풋을 고객측에 제출하고 관리했다. 그러나 이제는 소재 자체의 결과뿐 아니라 소재를 만들면서 나오는 제조 파라미터나 원재료의 파라미터도 디바이스에 직접적으로 영향을 미쳐 더 많고 자세한 데이터가 필요한 상황”이라고 밝혔다. 이는 제품의 두께, 수율, 신뢰성과 관련해 큰 문제를 일으킬 수도 있는 부분이다. 또한, 최근에는 대기의 온도, 습도 등 보관방법으로 인한 자연분해 문제도 대두되고 있다고 설명했다.

품질 체크를 위한 데이터 분석은 많이 자동화되긴 했으나 휴먼 에러나 빅데이터의 게더링 문제가 여전히 존재한다. 최 박사는 “미세한 품질 변화가 신규 제품에서 큰 문제를 일으킬 수 있기에 제품의 수율 등 데이터 통계에 기반한 원클릭 분석 시스템을 준비하고 있다”고 말했다.

그래도 삭제하시겠습니까?